# CMOS 8K x 8 ZEROPOWER SRAM

#### **DATA BRIEFING**

- INTEGRATED ULTRA LOW POWER SRAM, POWER-FAIL CONTROL CIRCUIT and BATTERY

- READ CYCLE TIME EQUALS WRITE CYCLE TIME

- AUTOMATIC POWER-FAIL CHIP DESELECT and WRITE PROTECTION

- CHOICE of TWO WRITE PROTECT VOLTAGES:

- $M48Z58: 4.5V \le V_{PFD} \le 4.75V$

- M48Z58Y: 4.2V ≤ V<sub>PFD</sub> ≤ 4.5V

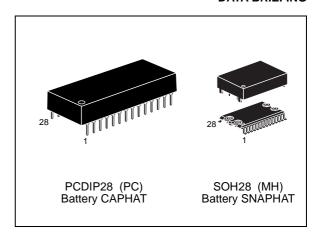

- SELF CONTAINED BATTERY in the CAPHAT DIP PACKAGE

- SMALL OUTLINE PACKAGE PROVIDES DIRECT CONNECTION for a SNAPHAT HOUSING CONTAINING the BATTERY

- SNAPHAT HOUSING (BATTERY) REPLACEABLE

- PIN and FUNCTION COMPATIBLE with JEDEC STANDARD 8K x 8 SRAMs

### **DESCRIPTION**

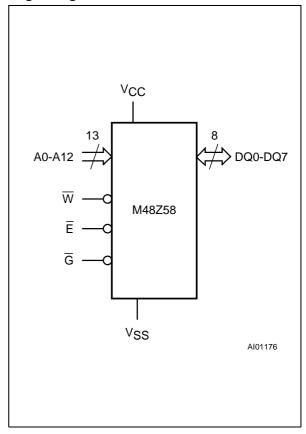

The M48Z58 ZEROPOWER<sup>®</sup> RAM is an 8K x 8 non-volatile static RAM that integrates power-fail deselect circuitry and battery control logic on a single die. The monolithic chip is available in two special packages to provide a highly integrated battery backed-up memory solution.

The M48Z58 is a non-volatile pin and function equivalent to any JEDEC standard 8K x 8 SRAM. It also easily fits into many ROM, EPROM, and EEPROM sockets, providing the non-volatility of PROMs without any requirement for special write timing or limitations on the number of writes that can be performed.

## **Logic Diagram**

B48Z58/507 1/2

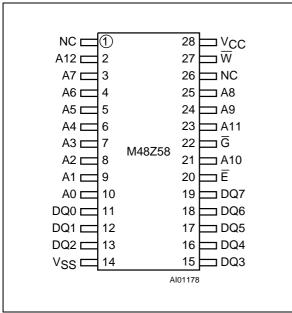

#### **DIP Pin Connections**

| NC [ 1               | $\overline{}$ | 28 ] V <sub>CC</sub> |

|----------------------|---------------|----------------------|

| A12 🛮 2              |               | 27 🛮 W               |

| A7 🛚 3               | M48Z58        | 26 NC                |

| A6 🛚 4               |               | 25 ] A8              |

| A5 [] 5              |               | 24 🛮 A9              |

| A4 [ 6               |               | 23 A11               |

| A3 [ 7               |               | 22 ] G               |

| A2 [ 8               |               | 21 A10               |

| A1 [ 9               |               | 20   Ē               |

| A0 [ 10              |               | 19 DQ7               |

| DQ0 [ 11             |               | 18 DQ6               |

| DQ1 [ 12             |               | 17 DQ5               |

| DQ2 [ 13             |               | 16 DQ4               |

| V <sub>SS</sub> [ 14 |               | 15 DQ3               |

|                      | A             | l01177               |

|                      |               |                      |

|                      |               |                      |

Warning: NC = Not Connected

## **SO Pin Connections**

Warning: NC = Not Connected

## **Signal Names**

| A0-A12          | Address Inputs        |  |

|-----------------|-----------------------|--|

| DQ0-DQ7         | Data Inputs / Outputs |  |

| Ē               | Chip Enable           |  |

| G               | Output Enable         |  |

| W               | Write Enable          |  |

| Vcc             | Supply Voltage        |  |

| V <sub>SS</sub> | Ground                |  |

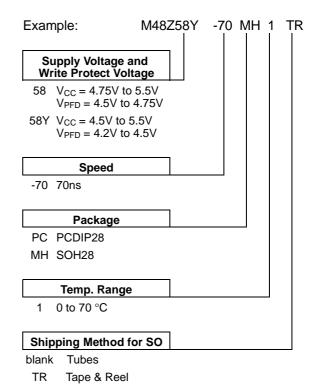

## **Ordering Information Scheme**

For a list of available options refer to the current Memory Shortform catalogue.

For further information on any aspect of this device, please contact the SGS-THOMSON Sales Office nearest to you.

**Note:** The SO and battery packages are shipped separately in plastic anti-static tubes. The SO package is also available to ship in Tape & Reel form. For the 28 lead SO, the battery package (i.e. SNAPHAT) part number is "M4Z28-BR00SH1".

47/