## General Description

The MAX2430 is a versatile, silicon RF power amplifier that operates directly from a 3V to 5.5V supply, making it suitable for 3-cell NiCd or 1-cell lithium-ion battery applications. It is designed for use in the 800MHz to 1000MHz frequency range and, at 915MHz, can produce +21dBm (125mW) of output power with greater than 32dB of gain at  $V_{CC} = 3.6V$ .

A unique shutdown function provides an off supply current of typically less than 1µA to save power during "idle slots" in time-division multiple-access (TDMA) transmissions. An external capacitor sets the RF output power envelope ramp time. External power control is also possible over a 15dB range. The amplifier's input is matched on-chip to  $50\Omega$ . The output is an open collector that is easily matched to a 50 $\Omega$  load with few external components.

The MAX2430 is ideal as a driver amplifier for portable and mobile telephone systems, or as a complete power amplifier for other low-cost applications, such as those in the 915MHz spread-spectrum ISM band. It is fabricated with Maxim's high-frequency bipolar transistor process, and comes in a thermally enhanced, 16-pin narrow SO package.

## **Applications**

**Digital Cordless Phones** 915MHz ISM-Band Applications **Two-Way Pagers** Wireless LANs Cellular Phones AM and FM Analog Transmitters

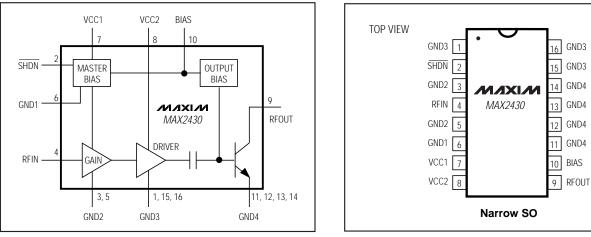

### **Functional Diagram**

## M/IXI/M

Maxim Integrated Products 1 For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800

## Features

- Operates Over the 800MHz to 1000MHz Frequency Range

- Delivers 125mW at 915MHz from 3.6V Supply (100mW typical from 3.0V supply)

- Operates Directly from 3-Cell NiCd or 1-Cell Lithium-Ion Battery

- Over 32dB Power Gain

- RF Power Envelope Ramping is Programmable with One External Capacitor

- Input Matched to 50Ω (VSWR < 2:1)</p>

- 15dB Output Power Control Range

- 1µA Typical Shutdown Current

## Ordering Information

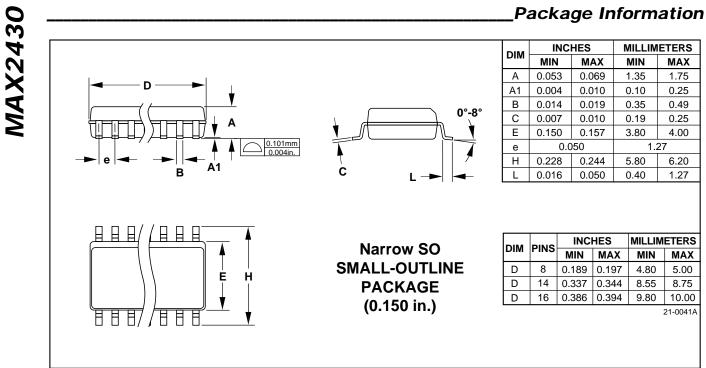

| PART       | TEMP. RANGE    | PIN-PACKAGE  |

|------------|----------------|--------------|

| MAX2430ISE | -20°C to +85°C | 16 Narrow SO |

### Pin Configuration

## **ABSOLUTE MAXIMUM RATINGS**

| VCC1, VCC2 | 6V                             |

|------------|--------------------------------|

| SHDN, BIAS | 0.3V, (V <sub>CC</sub> + 0.3V) |

| RFIN       |                                |

| PRFIN      | 3dBm                           |

Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )

| SO (derate 20mW/°C above +70°C)     | 1.6W      |

|-------------------------------------|-----------|

| Operating Temperature Range20°C     | to +85°C  |

| Storage Temperature Range           | io +160°C |

| Lead Temperature (soldering, 10sec) | +300°C    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = VCC1 = VCC2 = RFOUT = 3V \text{ to } 5.5V, \text{ GND1} = \text{GND2} = \text{GND3} = \text{GND4} = 0V, \overline{\text{SHDN}} = 2.2V, \text{BIAS} = \text{open}, \text{RFIN} = \text{open}, \text{T}_{A} = -20^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$

| PARAMETER               | SYMBOL    | CONDITIONS                           | MIN | TYP | MAX | UNITS |

|-------------------------|-----------|--------------------------------------|-----|-----|-----|-------|

| Supply Voltage Range    | Vcc       |                                      | 3   |     | 5.5 | V     |

| Supply Current          | Icc       | No RF input applied, $V_{CC} = 5.5V$ |     | 52  | 70  | mA    |

| Shutdown Supply Current | ICC(OFF)  | SHDN = low                           |     | 1   | 10  | μA    |

| BIAS Pin Voltage        | VBIAS     | BIAS pin open                        |     | 2.2 |     | V     |

| SHDN High Input         | VSHDN(HI) |                                      | 2.2 |     | Vcc | V     |

| SHDN Low Input          | VSHDN(LO) |                                      |     |     | 0.4 | V     |

| SHDN Bias Current       | ISHDN     | SHDN = V <sub>CC</sub>               |     |     | 18  | μΑ    |

#### **AC ELECTRICAL CHARACTERISTICS**

(MAX2430 evaluation kit, f = 915MHz, V<sub>CC</sub> = 3.6V,  $\overline{SHDN}$  = V<sub>CC</sub>, RFOUT matched to 50 $\Omega$  resistive load, output measurements taken after matching network, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                     | SYMBOL  | CONDITIONS                                                        | MIN | TYP  | MAX  | UNITS |

|-----------------------------------------------|---------|-------------------------------------------------------------------|-----|------|------|-------|

| Frequency Range                               |         | (Note 2)                                                          | 800 |      | 1000 | MHz   |

|                                               | Daup    | VCC = 3.6V                                                        | 20  | 21.4 |      | - dBm |

| POUT at 1dB Compression                       | P1dB    | $V_{CC} = 3.0V$                                                   | 19  | 20.4 |      |       |

| Power Gain                                    | Gp      | Prfin = -20dBm                                                    | 32  | 34   |      | dB    |

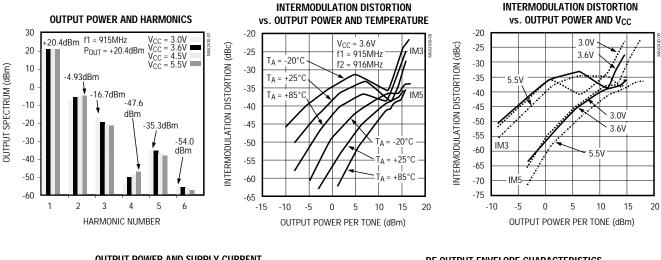

| Output IM3                                    | OIM3    | f1 = 915MHz, $f2 = 916MHz$ ,<br>P <sub>OUT</sub> per tone = 14dBm |     | -30  |      | dBc   |

| 2nd Harmonic                                  |         | Pout = P <sub>1dB</sub>                                           |     | -26  |      | dBc   |

| 3rd Harmonic                                  |         | Pout = P <sub>1dB</sub>                                           |     | -40  |      | dBc   |

| Efficiency                                    | η       | Pout = P1dB                                                       |     | 24   |      | %     |

| Supply Current                                | ICCRF   | Pout = P <sub>1dB</sub>                                           |     | 160  |      | mA    |

| Maximum Input VSWR                            | VSWRIN  | RFIN connected to 50 $\Omega$ source                              |     | 2:1  |      |       |

| Maximum Output Load<br>Mismatch               | VSWROUT | $V_{CC} = 3V$ to 5.5V, $P_{RFIN} \leq -10$ dBm (Note 3)           |     | 8:1  |      |       |

| Maximum Output Load<br>Mismatch for Stability | VSWROUT | $V_{CC} = 3V$ to 5.5V, $P_{RFIN} \leq -12dBm$ (Note 4)            |     | 6:1  |      |       |

| Noise Figure                                  | NF      |                                                                   |     | 7    |      | dB    |

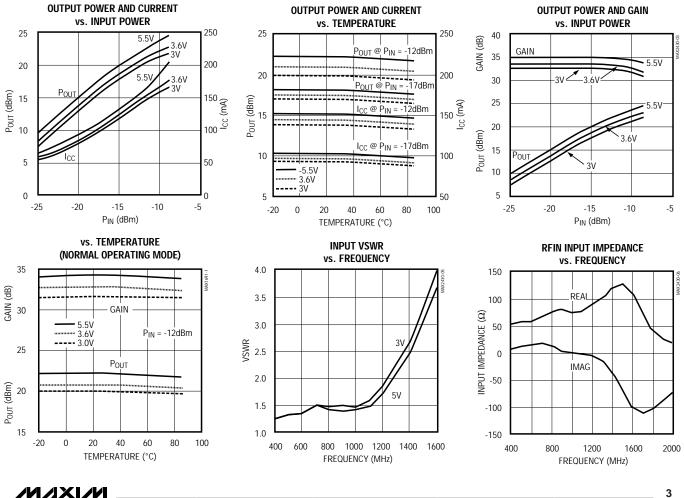

**Typical Operating Characteristics**

#### **AC ELECTRICAL CHARACTERISTICS**

(MAX2430 evaluation kit, f = 915MHz, V<sub>CC</sub> = 3.6V,  $\overline{SHDN} = V_{CC}$ , output matched to 50 $\Omega$  resistive load, output measurements taken after matching network,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER               | SYMBOL | CONDITIONS                                | MIN | TYP | MAX | UNITS |

|-------------------------|--------|-------------------------------------------|-----|-----|-----|-------|

| RFIN to RFOUT Isolation |        | $\overline{SHDN} = 0.4V, P_{IN} = -10dBm$ |     | 50  |     | dB    |

| Turn-On/Off Times       |        | BIAS pin capacitor C1 = 120pF             |     | 1   |     | us    |

|                         |        | BIAS pin capacitor C1 = 2.2nF             |     | 10  |     | μο    |

Note 1: Minimum and maximum parameters are guaranteed by design.

Note 2: For optimum performance at a given frequency, output matching network must be designed for maximum output power.

See Applications Information section. Operation outside this frequency range is possible but has not been characterized. Note 3: No damage to the device.

Note 4: All non-harmonically related outputs are more than 60dB below the desired signal for any electrical phase.

#### (MAX2430 evaluation kit, f = 915MHz, $V_{CC}$ = 3.6V, SHDN = $V_{CC}$ , output matched to 50 $\Omega$ resistive load, output measurements taken after matching network, $T_A = +25^{\circ}C$ , unless otherwise noted.)

## \_Typical Operating Characteristics (continued)

(MAX2430 evaluation kit, f = 915MHz,  $V_{CC}$  = 3.6V,  $\overline{SHDN}$  =  $V_{CC}$ , output matched to 50 $\Omega$  resistive load, output measurements taken after matching network,  $T_A$  = +25°C, unless otherwise noted.)

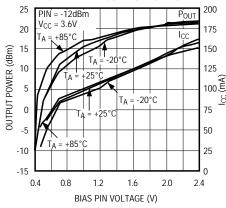

OUTPUT POWER AND SUPPLY CURRENT vs. EXTERNAL CONTROL VOLTAGE

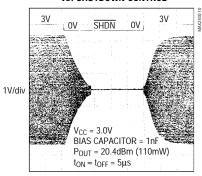

RF OUTPUT ENVELOPE CHARACTERISTICS vs. Shutdown Control

5µs/div

///XI//I

## \_Pin Description

| PIN          | NAME  | FUNCTION                                                                                                                                                                |  |

|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 15,<br>16 | GND3  | Driver Stage Ground. Connect directly to ground plane.                                                                                                                  |  |

| 2            | SHDN  | Shutdown Input (TTL/CMOS)                                                                                                                                               |  |

| 3, 5         | GND2  | Input Stage Ground. Connect directly to ground plane.                                                                                                                   |  |

| 4            | RFIN  | RF Input. Internally matched to $50\Omega$ . Requires series DC-blocking capacitor.                                                                                     |  |

| 6            | GND1  | Bias Circuitry Ground. Connect directly to ground plane.                                                                                                                |  |

| 7            | VCC1  | Bias Circuitry Supply. Connect to supply.<br>Bypass with 1000pF capacitor.                                                                                              |  |

| 8            | VCC2  | Driver Stage Output. Connect to supply through inductor (see <i>Applications Information</i> ).                                                                         |  |

| 9            | RFOUT | Output Transistor. Open Collector.                                                                                                                                      |  |

| 10           | BIAS  | Output Stage Bias Pin. Connect capacitor<br>to GND to control start-up power enve-<br>lope. Drive directly for power control (see<br><i>Applications Information</i> ). |  |

| 11–14        | GND4  | Output Stage Ground. Connect directly to ground plane.                                                                                                                  |  |

## \_Detailed Description

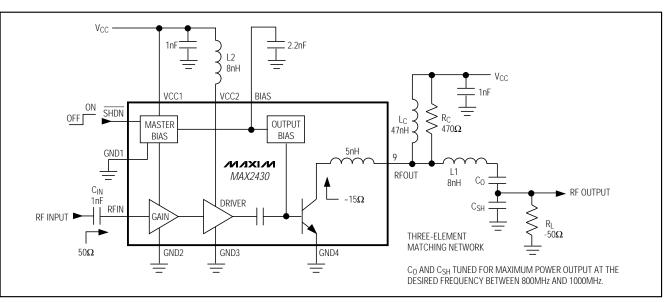

The MAX2430 consists of a large power output transistor driven by a capacitively coupled driver stage (see *Functional Diagram*). The driver and front-end gain stages are DC connected and biased on-chip from the master bias cell. The master bias cell also controls the output stage bias circuit. The input impedance at the RFIN pin is internally matched to  $50\Omega$ , while the output stage must be tuned and filtered externally for any narrow-band frequency range of interest between 800MHz and 1000MHz.

The driver amplifier requires an external inductor at the VCC2 pin to provide DC bias and proper matching to the output stage. This inductor's value depends on the frequency range of operation and will vary between 5nH and 22nH.

The output transistor at the RFOUT pin requires an external RF choke inductor connected to the supply for DC bias, and a matching network to transform the desired external load impedance to the optimal internal load impedance of approximately  $15\Omega$ .

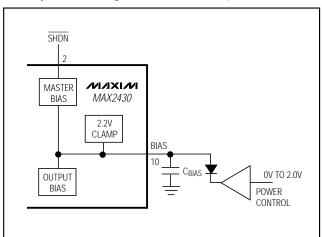

The MAX2430 includes a unique shutdown feature. The TTL/CMOS-compatible SHDN input allows the device to be shut down completely without the use of any external components. Also, the RF output power envelope ramp time can be programmed with a single external capacitor connected between the BIAS pin and ground. Pulling the shutdown pin (SHDN) high powers on the master bias circuit, which in turn charges the external capacitor tied to the BIAS pin using a controlled current. The voltage at BIAS controls the output power level, which ramps until the BIAS pin is internally clamped to approximately 2.2V. The envelope ramp-down time is controlled in a similar manner when the SHDN pin is pulled low.

Variable output power control over a 15dB range is also possible by forcing the voltage on the BIAS pin externally from 0.6V to 2.4V.

During the on state  $(\overline{SHDN} = high)$ , the power-supply bias current is typically 52mA with no RF applied to the input. During the off state  $(\overline{SHDN} = low)$ , the supply current is typically reduced to less than 1µA.

**MAX2430**

Figure 1. Typical Application Circuit

## Applications Information

#### **Output Matching**

The optimum internal load impedance seen by RFOUT is approximately  $15\Omega$ . This on-chip low drive impedance provides maximum power transfer and best efficiency under low (3V) supply conditions where the voltage-swing headroom is limited. For example, driving an output power of 21.3dBm (135mW) into  $50\Omega$  translates to a 7.35Vp-p swing at the output. An RF amplifier would require at least a 4.5V supply to drive a  $50\Omega$  load directly. However, driving 21.3dBm into  $15\Omega$  translates to 4.02Vp-p. The MAX2430 can achieve a voltage swing of 4.02Vp-p or 2.01Vp from a 3V supply voltage without saturating the output transistor.

Figure 1 shows the MAX2430 configured for 800MHz to 1000MHz operation. The output matching circuitry converts the desired 50 $\Omega$  load impedance to the 15 $\Omega$  optimal load seen by the output transistor's collector. This configuration uses a low-loss, controlled-Q inductor network. Starting from the RFOUT pin, this network consists of a series L (which includes the 5nH package parasitic inductance), series C, and shunt C. The design equations for this network are as follows:

- R1 = Output resistance as seen by the collector  $\sim 15\Omega$

- RL = Desired load resistance

The controlled-Q inductor network requires that

$R_L > R1$  and  $Q > \sqrt{(R_L / R1 - 1)}$ . Choose Q and compute matching components as given below:

Let

$$A = \sqrt{\left(R_{L} \times R1 - R1^{2}\right)}$$

$$X_{L} = Q \times R1$$

$$X_{Co} = X_{L} - A$$

$$X_{Csh} = R_{L} \times R1 / A$$

$$L1 = X_{L} / \omega - 5nH \text{ of package inductance}$$

$$C_{O} = \frac{1}{\omega X_{Co}}$$

$$C_{SH} = \frac{1}{\omega X_{Csh}}$$

where  $\omega$ equals the center frequency in radians/second. Recommended starting values for L1 and L2 are given in Table 1.

## Table 1. Recommended L1 and L2 Starting Values

| f = ω 2π(MHz)      | L1(nH) | L2(nH)   |

|--------------------|--------|----------|

| 400 to 600*        | 22     | 12       |

| 600 to 800*        | 15     | 8        |

| 800 to 1000        | 8      | 8        |

| *not characterized |        | ///XI//I |

6

An overall loaded  $Q \leq 5$  can be achieved with readily available surface-mount components. This network absorbs the parasitic elements of the surface-mount components in such a way that they do not negatively impact the stopband characteristics; in fact, they can improve the overall stopband attenuation with properly chosen components. High-Q components (Q > 100) that have self-resonance near the 3rd harmonic of the intended output frequency should provide good passband characteristics with low loss, while offering good attenuation of the undesired 2nd and 3rd harmonics that are generated. Note that most applications will require extra filtering components and good shielding after the matching network, to ensure absolute attenuation of out-of-band signals in order to meet out-of-band spurious suppression requirements.

#### **Output Mismatch Considerations**

The MAX2430 will typically withstand an output load mismatch of VSWR = 6:1 at any electrical phase without exhibiting oscillatory behavior over the entire supply voltage range of 3V to 5.5V. Resistor R<sub>C</sub> enhances stability under load mismatch conditions and does not affect normal operation of the circuit.

**BIAS** Pin

The voltage at the BIAS pin controls the output power transistor biasing. At BIAS = 0.6V, the output transistor is biased to Class C, resulting in low gain and relatively nonlinear power. Above 2V, the output stage is biased to Class AB. Note that changing the bias voltage may degrade the output transistor's stability.

The shutdown pin (SHDN) controls the master bias circuit, which in turn provides a control current of approximately  $\pm 500\mu$ A to the external capacitor connected to the BIAS pin. When SHDN transitions from low to high, the BIAS pin capacitor charges up and clamps at approximately 2.2V. When SHDN transitions from high to low, the BIAS pin capacitor is discharged to nearly ground. This results in a power-up/power-down ramping of the RF envelope, which can be approximated by the following equation:

tramp ≅CBIAS x 2.2V / 0.5mA = 4400Ω CBIAS

Therefore, a 2.2nF capacitor will give approximately 10µs ramp time.

The BIAS pin can also be used to control the final output power and gain over a 15dB range, by forcing the BIAS pin voltage externally between 0.6V and 2.4V. Note that the BIAS pin driver must be able to source/sink 700µA. Forcing the BIAS pin directly in this manner disrupts the RF envelope timing function. To avoid this, place a diode in series with the BIAS pin control circuit, as shown in Figure 2.

Note that when using the BIAS pin for power control, linearity is much degraded at the lower power levels.

Figure 2. Power-Control Application Using BIAS Pin