Features

# EVALUATION KIT MANUALS FOLLOW DATA SHEET Synchronous Rectifier for CPU Power

#### General Description

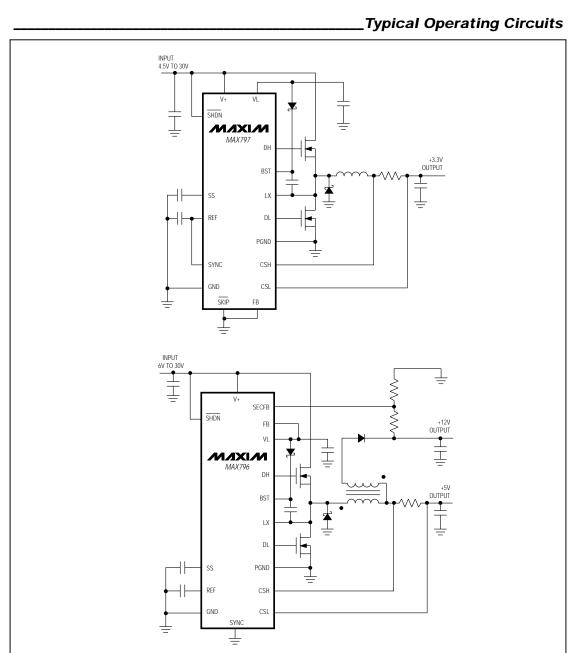

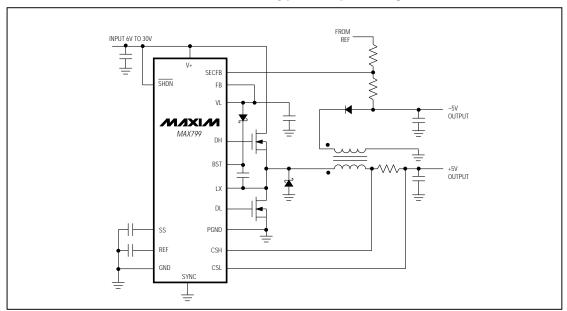

The MAX796/MAX797/MAX799 high-performance, stepdown DC-DC converters with single or dual outputs provide main CPU power in battery-powered systems. These buck controllers achieve 96% efficiency by using synchronous rectification and Maxim's proprietary Idle Mode™ control scheme to extend battery life at full-load (up to 10A) and no-load outputs. Excellent dynamic response corrects output transients caused by the latest dynamic-clock CPUs within five 300kHz clock cycles. Unique bootstrap circuitry drives inexpensive N-channel MOSFETs, reducing system cost and eliminating the crowbar switching currents found in some PMOS/NMOS switch designs.

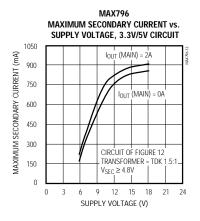

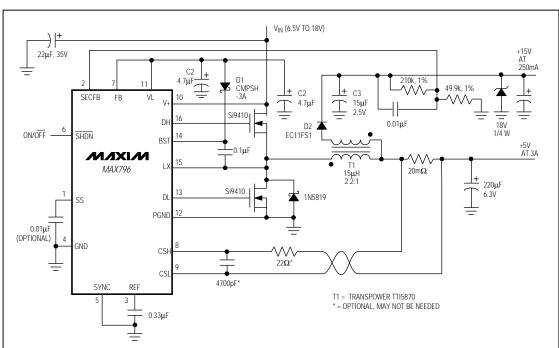

The MAX796/MAX799 are specially equipped with a secondary feedback input (SECFB) for transformer-based dual-output applications. This secondary feedback path improves cross-regulation of positive (MAX796) or negative (MAX799) auxiliary outputs.

The MAX797 has a logic-controlled and synchronizable fixed-frequency pulse-width-modulating (PWM) operating mode, which reduces noise and RF interference in sensitive mobile-communications and pen-entry applications. The SKIP override input allows automatic switchover to idle-mode operation (for high-efficiency pulse skipping) at light loads, or forces fixed-frequency mode for lowest noise at all loads.

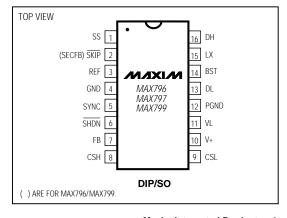

The MAX796/MAX797/MAX799 are all available in 16pin DIP and narrow SO packages. See the table below to compare these three converters.

| PART   | MAIN OUTPUT     | SPECIAL FEATURE                                     |

|--------|-----------------|-----------------------------------------------------|

| MAX796 | 3.3V/5V or adj. | Regulates positive secondary voltage (such as +12V) |

| MAX797 | 3.3V/5V or adj. | Logic-controlled low-noise mode                     |

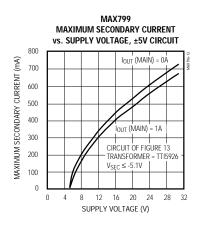

| MAX799 | 3.3V/5V or adj. | Regulates negative secondary voltage (such as -5V)  |

#### Applications

Notebook and Subnotebook Computers PDAs and Mobile Communicators

Cellular Phones

Idle Mode is a trademark of Maxim Integrated Products. †U.S. and foreign patents pending

♦ 96% Efficiency

- ♦ 4.5V to 30V Input Range

- ♦ 2.5V to 6V Adjustable Output

- ♦ Preset 3.3V and 5V Outputs (at up to 10A)

- **♦ Multiple Regulated Outputs**

- → +5V Linear-Regulator Output

- Precision 2.505V Reference Output

- ♦ Automatic Bootstrap Circuit

- ◆ 150kHz/300kHz Fixed-Frequency PWM Operation

- **♦ Programmable Soft-Start**

- ♦ 375µA Typ Quiescent Current (VIN = 12V, VOUT = 5V)

- ♦ 1µA Typ Shutdown Current

#### Ordering Information

| PART <sup>†</sup> | TEMP. RANGE     | PIN-PACKAGE    |

|-------------------|-----------------|----------------|

| MAX796CPE         | 0°C to +70°C    | 16 Plastic DIP |

| MAX796CSE         | 0°C to +70°C    | 16 Narrow SO   |

| MAX796C/D         | 0°C to +70°C    | Dice*          |

| MAX796EPE         | -40°C to +85°C  | 16 Plastic DIP |

| MAX796ESE         | -40°C to +85°C  | 16 Narrow SO   |

| MAX796MJE         | -55°C to +125°C | 16 CERDIP      |

Ordering Information continued at end of data sheet. \*Contact factory for dice specifications.

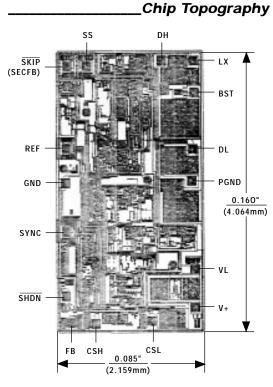

### Pin Configuration

MIXIM

Maxim Integrated Products 1

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800

### **ABSOLUTE MAXIMUM RATINGS**

| V+ to GND                              | 0.3V, +36V      |

|----------------------------------------|-----------------|

| GND to PGND                            | ±2V             |

| VL to GND                              | 0.3V, +7V       |

| BST to GND                             |                 |

| DH to LX                               |                 |

| LX to BST                              | 7V, +0.3V       |

| SHDN to GND                            | 0.3V, +36V      |

| SYNC, SS, REF, SECFB, SKIP, DL to GND. | 0.3V, VL + 0.3V |

| CSH, CSL to GND                        | 0.3V, +7V       |

| VL Short Circuit to GND                |                 |

| REF Short Circuit to GND               | Continuous      |

| VL Output Current                    | 50mA           |

|--------------------------------------|----------------|

| Continuous Power Dissipation (TA = + |                |

| SO (derate 8.70mW/°C above +70       | °C)696mW       |

| Plastic DIP (derate 10.53mW/°C at    |                |

| CERDIP (derate 10.00mW/°C abov       | re +70°C)800mW |

| Operating Temperature Ranges         |                |

| MAX79_C                              | 0°C to +70°C   |

| MAX79_E                              | 40°C to +85°C  |

| MAX79_MJE                            |                |

| Storage Temperature Range            |                |

| Lead Temperature (soldering, 10sec)  | +300°C         |

|                                      |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V+=15V,\ GND=PGND=0V,\ IVL=IREF=0A,\ T_A=0^{\circ}C\ to\ +70^{\circ}C\ for\ MAX79\_C,\ T_A=0^{\circ}C\ to\ +85^{\circ}C\ for\ MAX79\_E,\ T_A=-55^{\circ}C\ to\ +125^{\circ}C\ for\ MAX79\_M,\ unless otherwise\ noted.)$

| PARAMETER                                  | CONDITIONS                                                             |               |      | TYP   | MAX  | UNITS |

|--------------------------------------------|------------------------------------------------------------------------|---------------|------|-------|------|-------|

| +3.3V AND +5V STEP-DOWN                    | CONTROLLERS                                                            | •             |      |       |      | •     |

| Input Cumply Dange                         | MAX79_C                                                                |               | 4.5  |       | 30   | V     |

| Input Supply Range                         | MAX79_E                                                                | Z/M           | 5.0  |       | 30   | 7 °   |

| 5V Output Voltage (CSL)                    | 0mV < (CSH-CSL) < 80mV, FB = VL, 6V includes line and load regulation  | < V+ < 30V,   | 4.85 | 5.10  | 5.25 | V     |

| 3.3V Output Voltage (CSL)                  | 0mV < (CSH-CSL) < 80mV, FB = 0V, 4.5 includes line and load regulation | V < V+ < 30V, | 3.20 | 3.35  | 3.46 | V     |

| Nominal Adjustable Output<br>Voltage Range | External resistor divider                                              | -             | REF  |       | 6    | V     |

| Feedback Voltage                           | (CSH-CSL) = 0V                                                         |               | 2.43 | 2.505 | 2.57 | V     |

| Load Regulation                            | 0mV < (CSH-CSL) < 80mV                                                 |               |      | 2.5   |      | %     |

|                                            | 25mV < (CSH-CSL) < 80mV                                                |               |      | 1.5   |      | 7 "   |

| Line Regulation                            | 6V < V+ < 30V                                                          |               |      | 0.04  | 0.06 | %/V   |

| Current-Limit Voltage                      | CSH-CSL, positive                                                      |               | 80   | 100   | 120  | mV    |

| Current-Limit voltage                      | CSH-CSL, negative                                                      |               | -50  | -100  | -160 |       |

| SS Source Current                          |                                                                        |               | 2.5  | 4.0   | 6.5  | μΑ    |

| SS Fault Sink Current                      |                                                                        |               | 2.0  |       |      | mA    |

| FLYBACK/PWM CONTROLLE                      | R                                                                      | •             |      |       |      | •     |

| CECED Degulation Catagint                  | Falling edge, hysteresis = 15mV (MAX796)                               |               | 2.45 | 2.505 | 2.55 | V     |

| SECFB Regulation Setpoint                  | Falling edge, hysteresis = 20mV (MAX799)                               |               | 0.05 | 0     | 0.05 |       |

| INTERNAL REGULATOR AND                     | REFERENCE                                                              | •             |      |       |      | •     |

| VL Output Voltage                          | SHDN = 2V, 0mA < I <sub>VL</sub> < 25mA, 5.5V <                        | V+ < 30V      | 4.7  |       | 5.3  | V     |

| VL Fault Lockout Voltage                   | Rising edge, hysteresis = 15mV                                         |               | 3.8  |       | 4.1  | V     |

| VL/CSL Switchover Voltage                  | Rising edge, hysteresis = 25mV                                         |               | 4.2  |       | 4.7  | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=15V,\ GND=PGND=0V,\ IVL=IREF=0A,\ T_A=0^{\circ}C\ to\ +70^{\circ}C\ for\ MAX79\_C,\ T_A=0^{\circ}C\ to\ +85^{\circ}C\ for\ MAX79\_E,\ T_A=-55^{\circ}C\ to\ +125^{\circ}C\ for\ MAX79\_M,\ unless otherwise\ noted.)$

| PARAMETER                       | CONDITIONS                                     |                      | MIN      | TYP   | MAX  | UNITS |

|---------------------------------|------------------------------------------------|----------------------|----------|-------|------|-------|

| Reference Output Voltage        | No external load (Note 1)                      | MAX79_C              | 2.46     | 2.505 | 2.54 | V     |

| Reference Output Voltage        | No externarioad (Note 1)                       | MAX79_E/M            | 2.45     |       | 2.55 | 7 °   |

| Reference Fault Lockout Voltage | Falling edge                                   |                      | 1.8      |       | 2.3  | V     |

| Reference Load Regulation       | 0μA < I <sub>REF</sub> < 100μA                 |                      |          |       | 50   | mV    |

| CSL Shutdown Leakage Curren     | t SHDN = 0V, CSL = 6V, V+                      | = 0V or 30V, VL = 0V |          | 0.1   | 1    | μΑ    |

| V+ Shutdown Current             | SHDN = 0V, V+ = 30V,                           | MAX79_C              |          | 1     | 3    |       |

| V+ Shuldown Current             | CSL = 0V or 6V                                 | MAX79_E/M            |          | 1     | 5    | μA    |

| V+ Off-State Leakage Current    | FB = CSH = CSL = 6V,                           | MAX79_C              |          | 1     | 3    |       |

| v+ Oii-State Leakage Current    | VL switched over to CSL                        | MAX79_E/M            |          | 1     | 5    | μA    |

| Dropout Power Consumption       | V+ = 4V, CSL = 0V (Note 2)                     | )                    |          | 4     | 8    | mW    |

| Quiescent Power Consumption     | CSH = CSL = 6V                                 |                      |          | 4.8   | 6.6  | mW    |

| OSCILLATOR AND INPUTS/OU        | JTPUTS                                         |                      |          |       |      |       |

| Oscillator Fraguency            | SYNC = REF                                     |                      | 270 300  |       | 330  | kHz   |

| Oscillator Frequency            | SYNC = 0V or 5V                                |                      | 125      | 150   | 175  |       |

| SYNC High Pulse Width           |                                                |                      |          |       |      | ns    |

| SYNC Low Pulse Width            |                                                |                      |          |       |      | ns    |

| SYNC Rise/Fall Time             | Guaranteed by design                           |                      |          |       | 200  | ns    |

| Oscillator Sync Range           |                                                |                      |          |       | 340  | kHz   |

| Martin D. L. O. de              | SYNC = REF                                     |                      | 89       | 91    |      | %     |

| Maximum Duty Cycle              | SYNC = 0V or 5V                                |                      | 93       | 96    |      | 7 %   |

| lace at High Maltage            | SYNC                                           |                      | VL - 0.5 |       |      | .,    |

| Input High Voltage              | SHDN, SKIP                                     |                      | 2.0      |       |      | - V   |

| land the second second          | SYNC                                           |                      |          |       | 0.8  | .,    |

| Input Low Voltage               | SHDN, SKIP                                     |                      |          |       | 0.5  | - V   |

|                                 | SHDN, 0V or 30V                                | SHDN, OV or 30V      |          |       | 2.0  |       |

|                                 | SECFB, 0V or 4V                                | SECFB, 0V or 4V      |          |       | 0.1  | 1 .   |

| Input Current                   | SYNC, SKIP                                     |                      |          |       | 1.0  | μA    |

|                                 | CSH, CSL, CSH = CSL = 6V, device not shut down |                      |          |       | 50   | 1     |

|                                 | FB, FB = REF                                   |                      |          |       | ±100 | nA    |

| DL Sink/Source Current          | DL forced to 2V                                |                      |          | 1     |      | А     |

| DH Sink/Source Current          | DH forced to 2V, BST-LX = 4.5V                 |                      |          | 1     |      | А     |

| DL On-Resistance                | High or low                                    |                      |          |       | 7    | Ω     |

| DH On-Resistance                | DH On-Resistance High or low, BST-LX = 4.5V    |                      |          |       | 7    | Ω     |

**Note 1:** Since the reference uses VL as its supply, V+ line-regulation error is insignificant.

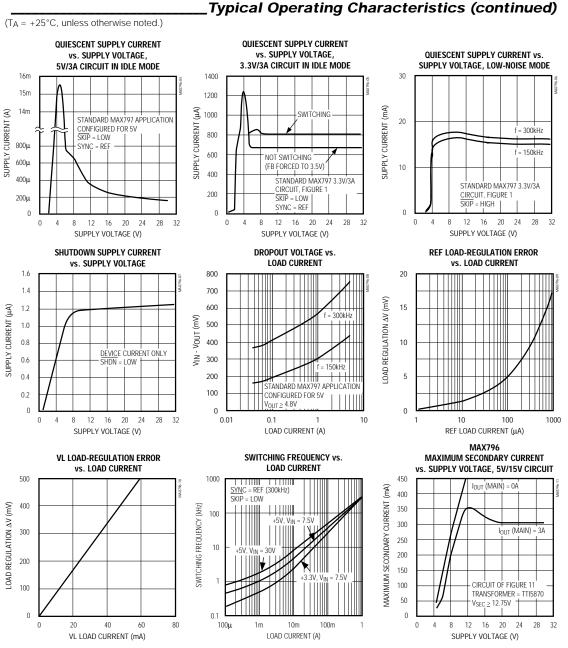

Note 2: At very low input voltages, quiescent supply current may increase due to excess PNP base current in the VL linear regulator. This occurs only if V+ falls below the preset VL regulation point (5V nominal). See the Quiescent Supply Current vs. Supply Voltage graph in the *Typical Operating Characteristics*.

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=15V, GND=PGND=0V, IVL=IREF=0A, T_A=-40^{\circ}C\ to +85^{\circ}C\ for\ MAX79\_E,\ unless\ otherwise\ noted.)\ (Note\ 3)$

| PARAMETER                                  | CONDITIONS                                                                            |       | TYP   | MAX  | UNITS  |  |

|--------------------------------------------|---------------------------------------------------------------------------------------|-------|-------|------|--------|--|

| +3.3V and +5V STEP-DOWN Co                 | ONTROLLERS                                                                            | •     |       |      | •      |  |

| Input Supply Range                         |                                                                                       | 5.0   |       | 30   | V      |  |

| 5V Output Voltage (CSL)                    | 0mV < (CSH - CSL) < 80mV, FB = VL, 6V < V+ < 30V, includes line and load regulation   |       | 5.10  | 5.40 | V      |  |

| 3.3V Output Voltage (CSL)                  | 0mV < (CSH - CSL) < 80mV, FB = VL, 4.5V < V+ < 30V, includes line and load regulation | 3.10  | 3.35  | 3.56 | V      |  |

| Nominal Adjustable Output<br>Voltage Range | External resistor divider                                                             | REF   |       | 6.0  | V      |  |

| Feedback Voltage                           | (CSH-CSL) = 0V                                                                        | 2.40  |       | 2.60 | V      |  |

| Line Regulation                            | 6V < V+ < 30V                                                                         |       | 0.04  | 0.06 | %/V    |  |

| Current-Limit Voltage                      | CSH - CSL, positive                                                                   | 70    |       | 130  | \/     |  |

| Current-Limit voltage                      | CSH - CSL, negative                                                                   | -40   | -100  | -160 | mV     |  |

| FLYBACK/PWM CONTROLLER                     | R                                                                                     | •     |       |      | •      |  |

| SECFB Regulation Setpoint                  | Falling edge, hysteresis = 15mV (MAX796)                                              | 2.40  |       | 2.60 | V      |  |

| SECEB Regulation Setpoint                  | Falling edge, hysteresis = 20mV (MAX799)                                              | -0.08 |       | 0.08 |        |  |

| INTERNAL REGULATOR AND                     | REFERENCE                                                                             | •     |       |      |        |  |

| VL Output Voltage                          | SHDN = 2V, 0mA < I <sub>VL</sub> < 25mA, 5.5V < V+ < 30V                              | 4.7   |       | 5.3  | V      |  |

| VL Fault Lockout Voltage                   | Rising edge, hysteresis = 15mV 3.                                                     |       |       | 4.05 | V      |  |

| VL/CSL Switchover Voltage                  | Rising edge, hysteresis = 25mV                                                        |       |       | 4.7  | V      |  |

| Reference Output Voltage                   | No external load (Note 1)                                                             |       | 2.505 | 2.57 | V      |  |

| Reference Load Regulation                  | 0μA < IREF < 100μA                                                                    |       |       | 50   | mV     |  |

| V+ Shutdown Current                        | SHDN = 0V, V+ = 30V, CSL = 0V or 6V                                                   |       | 1     | 10   | μΑ     |  |

| V+ Off-State Leakage Current               | FB = CSH = CSL = 6V, VL switched over to CSL                                          |       | 1     | 10   | μΑ     |  |

| Quiescent Power Consumption                |                                                                                       |       | 4.8   | 8.4  | mW     |  |

| OSCILLATOR AND INPUTS/OU                   | ITPUTS                                                                                | •     |       |      |        |  |

| Oscillator Frequency                       | SYNC = REF                                                                            | 250   | 300   | 350  | kHz    |  |

| Oscillator Frequency                       | SYNC = 0V or 5V                                                                       | 120   | 150   | 180  | T KITZ |  |

| SYNC High Pulse Width                      |                                                                                       | 250   |       |      | ns     |  |

| SYNC Low Pulse Width                       |                                                                                       | 250   |       |      | ns     |  |

| Oscillator Sync Range                      |                                                                                       | 210   |       | 320  | kHz    |  |

| Maximum Duty Cycle                         | SYNC = REF                                                                            | 89    | 91    |      | %      |  |

| Maximum Duty Cycle                         | SYNC = 0V or 5V                                                                       | 93    | 96    |      | /0     |  |

| DL On-Resistance                           | High or low                                                                           |       |       | 7    | Ω      |  |

| DH On-Resistance                           | High or low, BST - LX = 4.5V                                                          |       |       | 7    | Ω      |  |

**Note 3:** All -40°C to +85°C specifications above are guaranteed by design.

MIXIM

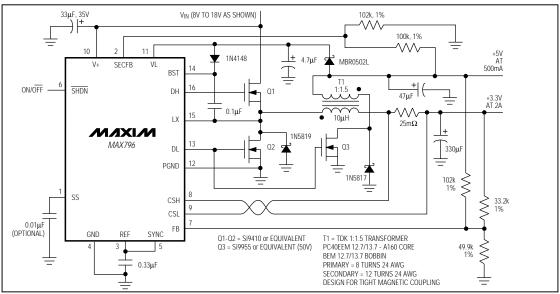

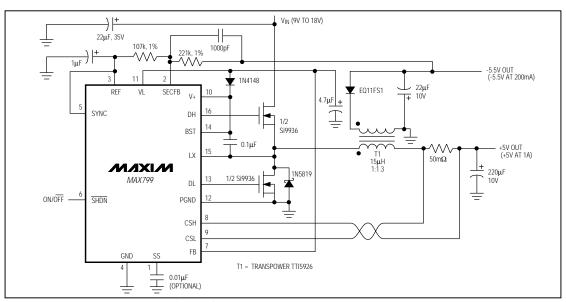

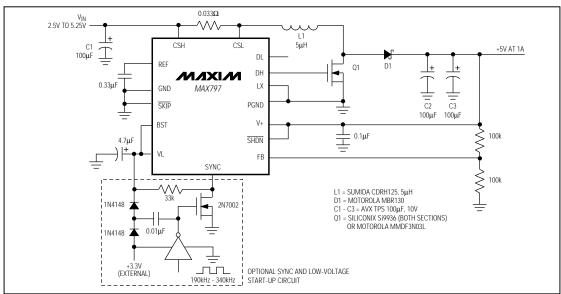

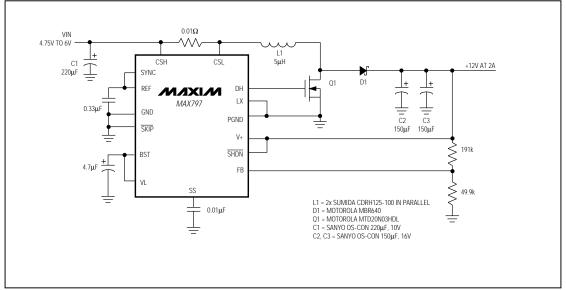

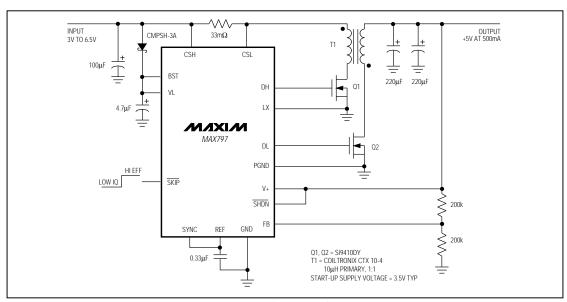

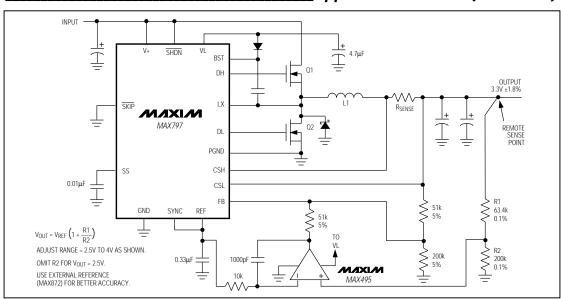

### Typical Operating Circuits (continued)

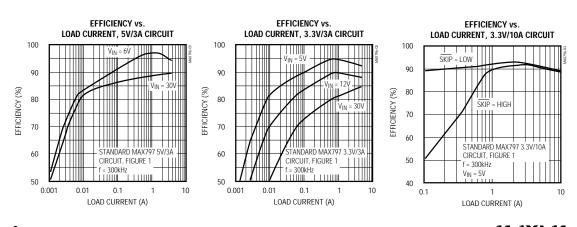

### \_Typical Operating Characteristics

( $T_A = +25^{\circ}C$ , unless otherwise noted.)

### \_Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, unless otherwise noted.)$

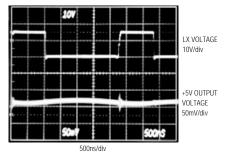

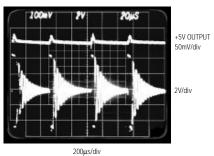

#### PULSE-WIDTH-MODULATION MODE WAVEFORMS

I<sub>LOAD</sub> = 1A, V<sub>IN</sub> = 16V, CIRCUIT OF FIGURE 1

#### **IDLE-MODE WAVEFORMS**

I<sub>LOAD</sub> = 100mA, V<sub>IN</sub> = 10V, CIRCUIT OF FIGURE 1

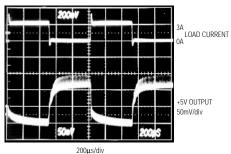

#### +5V LOAD-TRANSIENT RESPONSE

V<sub>IN</sub> = 15V, CIRCUIT OF FIGURE 1

### Pin Description

| PIN | NAME                         | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SS                           | Soft-Start timing capacitor connection. Ramp time to full current limit is approximately 1ms/nF.                                                                                                                                                                                                                                                                                                                                                           |

| 2   | SECFB<br>(MAX796/<br>MAX799) | Secondary winding Feedback input. Normally connected to a resistor divider from an auxiliary output.  Don't leave SECFB unconnected.  MAX796: SECFB regulates at VSECFB = 2.505V. Tie to VL if not used.  MAX799: SECFB regulates at VSECFB = 0V. Tie to a negative voltage through a high-value current-limiting resistor (I <sub>MAX</sub> = 100µA) if not used.                                                                                         |

|     | SKIP<br>(MAX797)             | Disables pulse-skipping mode when high. Connect to GND for normal use. <b>Don't leave SKIP</b> unconnected. With SKIP grounded, the device will <i>automatically</i> change from pulse-skipping operation to full PWM operation when the load current exceeds approximately 30% of maximum. (See Table 3.)                                                                                                                                                 |

| 3   | REF                          | Reference voltage output. Bypass to GND with 0.33µF minimum.                                                                                                                                                                                                                                                                                                                                                                                               |

| 4   | GND                          | Low-noise analog Ground and feedback reference point.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5   | SYNC                         | Oscillator Synchronization and frequency select. Tie to GND or VL for 150kHz operation; tie to REF for 300kHz operation. A high-to-low transition begins a new cycle. Drive SYNC with 0V to 5V logic levels (see the <i>Electrical Characteristics</i> table for V <sub>IH</sub> and V <sub>IL</sub> specifications). SYNC capture range is 190kHz to 340kHz guaranteed.                                                                                   |

| 6   | SHDN                         | Shutdown control input, active low. Logic threshold is set at approximately 1V (V <sub>TH</sub> of an internal N-channel MOSFET). Tie SHDN to V+ for automatic start-up.                                                                                                                                                                                                                                                                                   |

| 7   | FB                           | <ul> <li>Feedback input. Regulates at FB = REF (approximately 2.505V) in adjustable mode. FB is a Dual-Mode™ input that also selects the fixed output voltage settings as follows:</li> <li>Connect to GND for 3.3V operation.</li> <li>Connect to VL for 5V operation.</li> <li>Connect FB to a resistor divider for adjustable mode. FB can be driven with +5V rail-to-rail logic in order to change the output voltage under system control.</li> </ul> |

| 8   | CSH                          | Current-Sense input, High side. Current-limit level is 100mV referred to CSL.                                                                                                                                                                                                                                                                                                                                                                              |

| 9   | CSL                          | Current-Sense input, Low side. Also serves as the feedback input in fixed-output modes.                                                                                                                                                                                                                                                                                                                                                                    |

| 10  | V+                           | Battery voltage input (4.5V to 30V). Bypass V+ to PGND close to the IC with a $0.1\mu F$ capacitor. Connects to a linear regulator that powers VL.                                                                                                                                                                                                                                                                                                         |

| 11  | VL                           | 5V Internal linear-regulator output. VL is also the supply voltage rail for the chip. VL is switched to the output voltage via CSL (V <sub>CSL</sub> > 4.5V) for automatic bootstrapping. Bypass to GND with 4.7μF. VL can supply up to 5mA for external loads.                                                                                                                                                                                            |

| 12  | PGND                         | Power Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13  | DL                           | Low-side gate-drive output. Normally drives the synchronous-rectifier MOSFET. Swings 0V to VL.                                                                                                                                                                                                                                                                                                                                                             |

| 14  | BST                          | Boost capacitor connection for high-side gate drive (0.1µF).                                                                                                                                                                                                                                                                                                                                                                                               |

| 15  | LX                           | Switching node (inductor) connection. Can swing 2V below ground without hazard.                                                                                                                                                                                                                                                                                                                                                                            |

| 16  | DH                           | High-side gate-drive output. Normally drives the main buck switch. DH is a floating driver output that swings from LX to BST, riding on the LX switching-node voltage.                                                                                                                                                                                                                                                                                     |

Dual Mode is a trademark of Maxim Integrated Products.

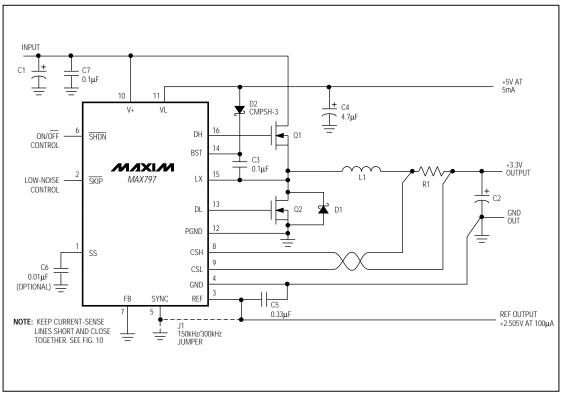

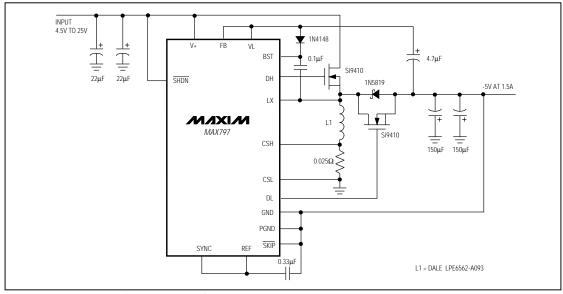

#### \_Standard Application Circuit

It is easy to adapt the basic MAX797 single-output 3.3V buck converter (Figure 1) to meet a wide range of applications with inputs up to 28V (limited by choice of external MOSFET). Simply substitute the appropriate components from Table 1. These circuits represent a good set of tradeoffs between cost, size, and efficiency while staying within the worst-case specification limits for stress-related parameters such as capacitor ripple current. Each of these circuits is rated for a continuous load current at TA = +85°C, as shown. The 1A, 2A and 10A applications can withstand a continuous output short-circuit to ground. The 3A and 5A applications can

withstand a short circuit of many seconds duration, but the synchronous-rectifier MOSFET overheats, exceeding the manufacturer's ratings for junction temperature by 50°C or more.

If the 3A or 5A circuit must be guaranteed to withstand a continuous output short circuit indefinitely, see the section *MOSFET Switches* under *Selecting Other Components*. Don't change the frequency of these circuits without first recalculating component values (particularly inductance value at maximum battery voltage).

Figure 1. Standard 3.3V Application Circuit

**Table 1. Component Selection for Standard 3.3V Applications**

| COMPONENT              | LOAD CURRENT                                        |                                                   |                                                  |                                                  |                                                    |  |  |

|------------------------|-----------------------------------------------------|---------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------------------------------------------------|--|--|

| COMPONENT              | 1A                                                  | 2A                                                | 3A                                               | 4A                                               | 10A                                                |  |  |

| Input Range            | 4.75V to 18V                                        | 4.75V to 18V                                      | 4.75V to 28V                                     | 4.75V to 24V                                     | 4.5V to 6V                                         |  |  |

| Application            | PDA                                                 | Sub-Notebook                                      | Notebook                                         | High-End Notebook                                | Desktop 5V-to-3V                                   |  |  |

| Frequency              | 150kHz                                              | 300kHz                                            | 300kHz                                           | 300kHz                                           | 300kHz                                             |  |  |

| Q1 High-Side<br>MOSFET | International Rectifier 1/2 IRF7101                 | Motorola 1/2<br>MMDF3N03HD or 1/2<br>Si9936       | Motorola<br>MMSF5N03HD or<br>Si9410              | Motorola<br>MTD20N03HDL<br>DPAK                  | Motorola<br>MTD75N03HDL<br>D <sup>2</sup> PAK      |  |  |

| Q2 Low-Side<br>MOSFET  | International Rectifier 1/2 IRF7101                 | Motorola 1/2<br>MMDF3N03HD or 1/2<br>Si9936       | Motorola<br>MMSF5N03HD or<br>Si9410              | Motorola<br>MTD20N03HDL<br>DPAK                  | Motorola<br>MTD75N03HDL<br>D <sup>2</sup> PAK      |  |  |

| C1 Input<br>Capacitor  | 22µF, 35V AVX TPS<br>or Sprague 595D                | 2 x 22μF, 35V AVX<br>TPS or Sprague 595D          | 2 x 22µF, 35V AVX<br>TPS or Sprague 595D         | 4 x 22μF, 35V AVX<br>TPS or Sprague 595D         | 2 x 220µF, 10V<br>Sanyo OS-CON<br>10SA220M         |  |  |

| C2 Output<br>Capacitor | 150µF, 10V AVX TPS<br>or Sprague 595D               | 150μF, 10V AVX TPS<br>or Sprague 595D             | 220µF, 10V AVX TPS<br>or Sprague 595D            | 3 x 220µF, 10V AVX<br>TPS or Sprague 595D        | 4 x 220μF, 10V<br>Sanyo OS-CON<br>10SA220M         |  |  |

| D1 Rectifier           | 1N5817 Motorola<br>MBR0502L SOD-89                  | 1N5817 NIEC<br>EC10QS02L or<br>Motorola MBRS130T3 | 1N5819 NIEC<br>EC10QS03 or<br>Motorola MBRS130T3 | 1N5821 NIEC<br>NSQ03A04 or<br>Motorola MBRS340T3 | 1N5820 NIEC<br>NSQ03A02, or<br>Motorola MBRS340T3  |  |  |

| R1 Resistor            | 0.062 <b>Ω</b> IRC<br>LR2010-01-R062                | 0.039 <b>Ω</b> IRC<br>LR2010-01-R039              | 0.025 <b>Ω</b> IRC<br>LR2010-01-R025             | 0.015 <b>Ω</b> IRC<br>LR2010-01-015              | 3 x 0.02Ω IRC<br>LR2010-01-R020<br>(3 in parallel) |  |  |

| L1 Inductor            | 47µH, 1.2A Ferrite or<br>Kool-Mu<br>Sumida CD75-470 | 33µH, 2.2A Ferrite<br>Dale LPE6562-330MB          | 10µH, 3A Ferrite<br>Sumida CDRH125               | 4.7µH, 5.5A Ferrite<br>Coilcraft DO3316-472      | 1.5μH, 11A, 3.5mΩ<br>Coiltronics<br>CTX03-12357-1  |  |  |

**Table 2. Component Suppliers**

| MANUEACTURER            | LICA DUONE      | FACTORY FAX      |  |  |

|-------------------------|-----------------|------------------|--|--|

| MANUFACTURER            | USA PHONE       | [Country Code]   |  |  |

| AVX                     | (803) 946-0690  | [1] 803-626-3123 |  |  |

| Central Semiconductor   | (516) 435-1110  | [1] 516-435-1824 |  |  |

| Coilcraft               | (847) 639-6400  | [1] 847-639-1469 |  |  |

| Coiltronics             | (561) 241-7876  | [1] 561-241-9339 |  |  |

| Dale                    | (605) 668-4131  | [1] 605-665-1627 |  |  |

| International Rectifier | (310) 322-3331  | [1] 310-322-3332 |  |  |

| IRC                     | (512) 992-7900  | [1] 512-992-3377 |  |  |

| Matsuo                  | (714) 969-2491  | [1] 714-960-6492 |  |  |

| Motorola                | (602) 303-5454  | [1] 602-994-6430 |  |  |

| Murata-Erie             | (814) 237-1431  | [1] 814-238-0490 |  |  |

| IVIGITATA-ETIE          | (800) 831-9172  | [1] 014-230-0470 |  |  |

| NIEC                    | (805) 867-2555* | [81] 3-3494-7414 |  |  |

| Sanyo                   | (619) 661-6835  | [81] 7-2070-1174 |  |  |

| Siliconix               | (408) 988-8000  | [1] 408-970-3950 |  |  |

| SIIICUTIIX              | (800) 554-5565  | [1] 400-970-3930 |  |  |

| Sprague                 | (603) 224-1961  | [1] 603-224-1430 |  |  |

| Sumida                  | (847) 956-0666  | [81] 3-3607-5144 |  |  |

| TDK                     | (847) 390-4461  | {1} 847-390-4405 |  |  |

| Transpower Technologies | (702) 831-0140  | [1] 702-831-3521 |  |  |

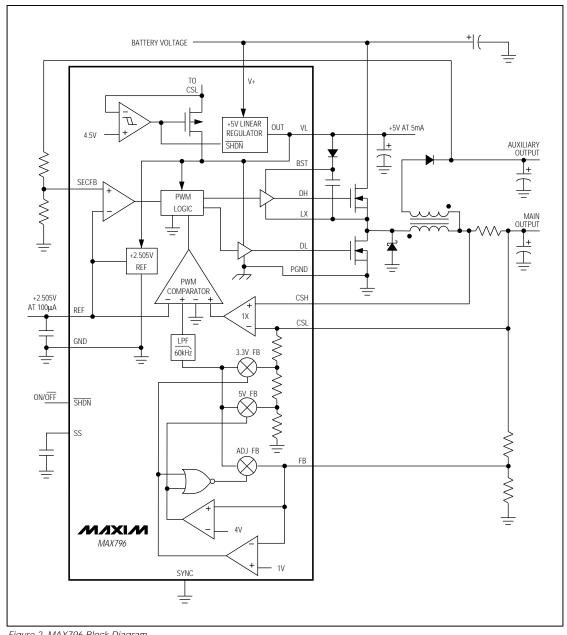

### \_Detailed Description

The MAX796 is a BiCMOS, switch-mode power-supply controller designed primarily for buck-topology regulators in battery-powered applications where high efficiency and low quiescent supply current are critical. The MAX796 also works well in other topologies such as boost, inverting, and CLK due to the flexibility of its floating high-speed gate driver. Light-load efficiency is enhanced by automatic idle-mode operation—a variable-frequency pulse-skipping mode that reduces losses due to MOSFET gate charge. The step-down power-switching circuit consists of two N-channel MOSFETs, a rectifier, and an LC output filter. The output voltage is the average of the AC voltage at the switching node, which is adjusted and regulated by changing the duty cycle of the MOSFET switches. The gate-drive signal to the N-channel high-side MOSFET must exceed the battery voltage and is provided by a flying capacitor boost circuit that uses a 100nF capacitor connected to BST.

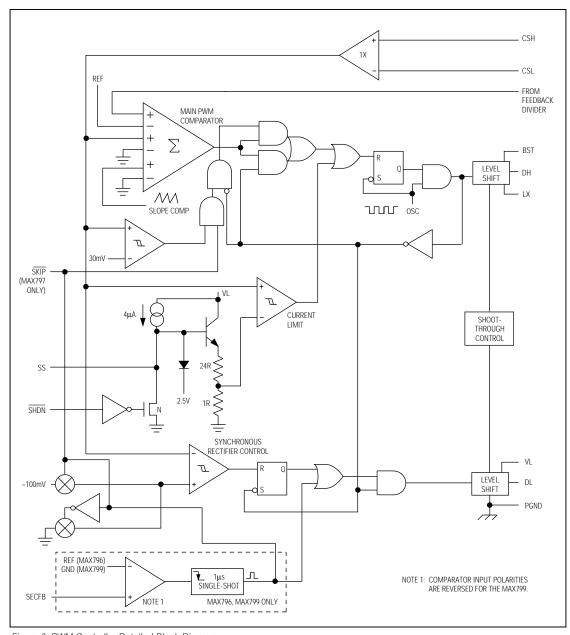

The MAX796 contains nine major circuit blocks, which are shown in Figure 2.

<sup>\*</sup> Distributor

Figure 2. MAX796 Block Diagram

NIXIN

PWM Controller Blocks:

- Multi-Input PWM Comparator

- Current-Sense Circuit

- PWM Logic Block

- Dual-Mode Internal Feedback Mux

- Gate-Driver Outputs

- Secondary Feedback Comparator

#### Bias Generator Blocks:

- +5V Linear Regulator

- Automatic Bootstrap Switchover Circuit

- +2.505V Reference

These internal IC blocks aren't powered directly from the battery. Instead, a +5V linear regulator steps down the battery voltage to supply both the IC internal rail (VL pin) as well as the gate drivers. The synchronous-switch gate driver is directly powered from +5V VL, while the high-side-switch gate driver is indirectly powered from VL via an external diode-capacitor boost circuit. An automatic bootstrap circuit turns off the +5V linear regulator and powers the IC from its output voltage if the output is above 4.5V.

#### **PWM Controller Block**

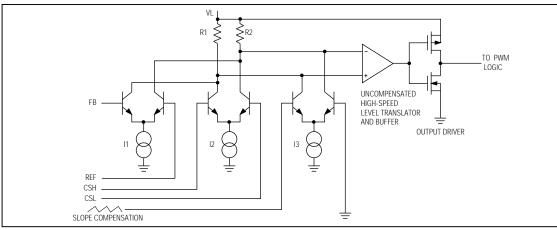

The heart of the current-mode PWM controller is a multi-input open-loop comparator that sums three signals: output voltage error signal with respect to the reference voltage, current-sense signal, and slope compensation ramp (Figure 3). The PWM controller is a direct summing type, lacking a traditional error amplifier and the phase shift associated with it. This direct-summing configuration approaches the ideal of cycle-by-cycle control over the output voltage.

Under heavy loads, the controller operates in full PWM mode. Each pulse from the oscillator sets the main PWM latch that turns on the high-side switch for a period determined by the duty factor (approximately V<sub>OUT</sub>/V<sub>IN</sub>). As the high-switch turns off, the synchronous rectifier latch is set. 60ns later the low-side switch turns on, and stays on until the beginning of the next clock cycle (in continuous mode) or until the inductor current crosses zero (in discontinuous mode). Under fault conditions where the inductor current exceeds the 100mV current-limit threshold, the high-side latch resets and the high-side switch turns off.

At light loads (SKIP = low), the inductor current fails to exceed the 30mV threshold set by the minimum-current comparator. When this occurs, the controller goes into idle mode, skipping most of the oscillator pulses in order to reduce the switching frequency and cut back gate-charge losses. The oscillator is effectively gated off at light loads because the minimum-current comparator immediately resets the high-side latch at the

**Table 3. Operating-Mode Truth Table**

| ·    |      |                 |                     |                                                                                                                 |  |  |

|------|------|-----------------|---------------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| SHDN | SKIP | LOAD<br>CURRENT | MODE<br>NAME        | DESCRIPTION                                                                                                     |  |  |

| Low  | Х    | X               | Shutdown            | All circuit blocks<br>turned off; supply<br>current = 1µA typ                                                   |  |  |

| High | Low  | Low,<br><10%    | Idle                | Pulse-skipping;<br>supply current =<br>700µA typ at V <sub>IN</sub> =<br>10V; discontinuous<br>inductor current |  |  |

| High | Low  | Medium,<br><30% | Idle                | Pulse-skipping;<br>continuous inductor<br>current                                                               |  |  |

| High | Low  | High,<br>>30%   | PWM                 | Constant-frequency<br>PWM; continuous<br>inductor current                                                       |  |  |

| High | High | Х               | Low Noise*<br>(PWM) | Constant-frequency<br>PWM regardless of<br>load; continuous<br>inductor current<br>even at no load              |  |  |

<sup>\*</sup> MAX796/MAX799 have no SKIP pin and therefore can't go into low-noise mode.

X = Don't Care

beginning of each cycle, unless the feedback signal falls below the reference voltage level.

When in PWM mode, the controller operates as a fixed-frequency current-mode controller where the duty ratio is set by the input/output voltage ratio. The current-mode feedback system regulates the peak inductor current as a function of the output voltage error signal. Since the average inductor current is nearly the same as the peak current, the circuit acts as a switch-mode transconductance amplifier and pushes the second output LC filter pole, normally found in a duty-factor-controlled (voltage-mode) PWM, to a higher frequency. To preserve inner-loop stability and eliminate regenerative inductor current "staircasing," a slope-compensation ramp is summed into the main PWM comparator to reduce the apparent duty factor to less than 50%.

The relative gains of the voltage- and current-sense inputs are weighted by the values of current sources that bias three differential input stages in the main PWM comparator (Figure 4). The relative gain of the voltage comparator to the current comparator is internally fixed at K = 2:1. The resulting loop gain (which is relatively low) determines the 2.5% typical load regulation error. The low loop-gain value helps reduce output filter capacitor size and cost by shifting the unity-gain crossover to a lower frequency.

Figure 3. PWM Controller Detailed Block Diagram

Figure 4. Main PWM Comparator Block Diagram

The output filter capacitor C2 sets a dominant pole in the feedback loop. This pole must roll off the loop gain to unity before the zero introduced by the output capacitor's parasitic resistance (ESR) is encountered (see *Design Procedure* section). A 60kHz pole-zero cancellation filter provides additional rolloff above the unity-gain crossover. This internal 60kHz lowpass compensation filter cancels the zero due to the filter capacitor's ESR. The 60kHz filter is included in the loop in both fixed- and adjustable-output modes.

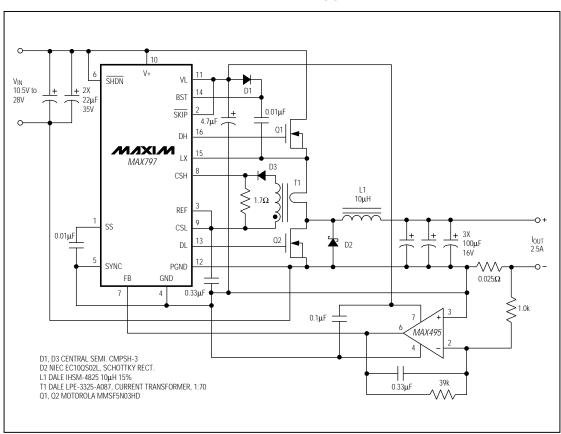

#### Synchronous-Rectifier Driver (DL Pin)

Synchronous rectification reduces conduction losses in the rectifier by shunting the normal Schottky diode with a low-resistance MOSFET switch. The synchronous rectifier also ensures proper start-up of the boost-gate driver circuit. If you must omit the synchronous power MOSFET for cost or other reasons, replace it with a small-signal MOSFET such as a 2N7002.

If the circuit is operating in continuous-conduction mode, the DL drive waveform is simply the complement of the DH high-side drive waveform (with controlled dead time to prevent cross-conduction or "shoot-through"). In discontinuous (light-load) mode, the synchronous switch is turned off as the inductor current falls through zero. The synchronous rectifier works under all operating conditions, including idle mode. The synchronous-switch timing is further controlled by the secondary feedback (SECFB) signal in order to improve multiple-output cross-regulation (see Secondary Feedback-Regulation Loop section).

#### Internal VL and REF Supplies

An internal regulator produces the 5V supply (VL) that powers the PWM controller, logic, reference, and other blocks within the MAX796. This +5V low-dropout linear regulator can supply up to 5mA for external loads, with a reserve of 20mA for gate-drive power. Bypass VL to GND with 4.7 $\mu$ F. **Important**: VL must not be allowed to exceed 6V. Measure VL with the main output fully loaded. If VL is being pumped up above 5.5V, the probable cause is either excessive boost-diode capacitance or excessive ripple at V+. Use only small-signal diodes for D2 (1N4148 preferred) and bypass V+ to PGND with 0.1 $\mu$ F directly at the package pins.

The 2.505V reference (REF) is accurate to  $\pm 1.6\%$  over temperature, making REF useful as a precision system reference. Bypass REF to GND with  $0.33\mu F$  minimum. REF can supply up to 1mA for external loads. However, if tight-accuracy specs for either VOUT or REF are essential, avoid loading REF with more than  $100\mu A$ . Loading REF reduces the main output voltage slightly, according to the reference-voltage load regulation error. In MAX799 applications, ensure that the SECFB divider doesn't load REF heavily.

When the main output voltage is above 4.5V, an internal P-channel MOSFET switch connects CSL to VL while simultaneously shutting down the VL linear regulator. This action bootstraps the IC, powering the internal circuitry from the output voltage, rather than through a linear regulator from the battery. Bootstrapping reduces power dissipation caused by gate-charge and quiescent losses by providing that power from a 90%-efficient switch-mode source, rather than from a 50%-efficient linear regulator.

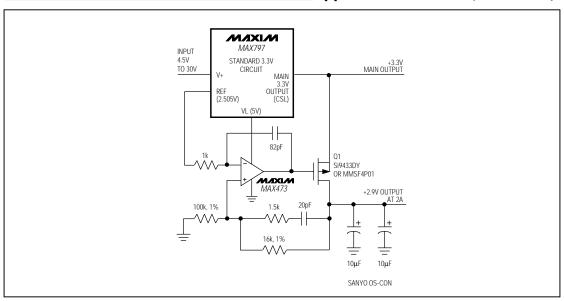

It's often possible to achieve a bootstrap-like effect, even for circuits that are set to V<sub>OUT</sub> < 4.5V, by powering VL from an external-system +5V supply. To achieve this pseudo-bootstrap, add a Schottky diode between the external +5V source and VL, with the cathode to the VL side. This circuit provides a 1% to 2% efficiency boost and also extends the minimum battery input to less than 4V. The external source must be in the range of 4.8V to 6V. Another way to achieve a pseudo-bootstrap is to add an extra flyback winding to the main inductor to generate the +5V bootstrap source, as shown in the +3.3V/+5V Dual-Output Application (Figure 12).

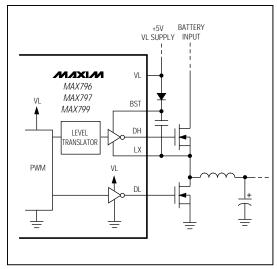

#### Boost High-Side Gate-Driver Supply (BST Pin)

Gate-drive voltage for the high-side N-channel switch is generated by a flying-capacitor boost circuit as shown in Figure 5. The capacitor is alternately charged from the VL supply and placed in parallel with the high-side MOSFET's gate-source terminals.

On start-up, the synchronous rectifier (low-side MOSFET) forces LX to 0V and charges the BST capacitor to 5V. On the second half-cycle, the PWM turns on the high-side MOSFET by closing an internal switch between BST and DH. This provides the necessary enhancement voltage to turn on the high-side switch, an action that "boosts" the 5V gate-drive signal above the battery voltage.

Ringing seen at the high-side MOSFET gate (DH) in discontinuous-conduction mode (light loads) is a natural operating condition, and is caused by the residual energy in the tank circuit formed by the inductor and stray capacitance at the switching node LX. The gate-driver negative rail is referred to LX, so any ringing there is directly coupled to the gate-drive output.

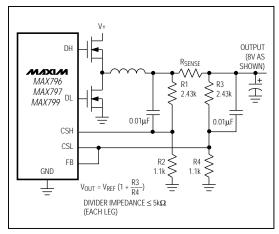

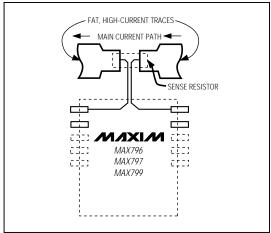

### Current-Limiting and Current-Sense Inputs (CSH and CSL)

The current-limit circuit resets the main PWM latch and turns off the high-side MOSFET switch whenever the voltage difference between CSH and CSL exceeds 100mV. This limiting is effective for both current flow directions, putting the threshold limit at ±100mV. The tolerance on the positive current limit is ±20%, so the external low-value sense resistor must be sized for 80mV/R1 to guarantee enough load capability, while components must be designed to withstand continuous current stresses of 120mV/R1.

For breadboarding purposes or very high-current applications, it may be useful to wire the current-sense inputs with a twisted pair rather than PC traces. This twisted pair needn't be anything special, perhaps two pieces of wire-wrap wire twisted together.

Figure 5. Boost Supply for Gate Drivers

#### Oscillator Frequency and Synchronization (SYNC Pin)

The SYNC input controls the oscillator frequency. Connecting SYNC to GND or to VL selects 150kHz operation; connecting SYNC to REF selects 300kHz. SYNC can also be used to synchronize with an external 5V CMOS or TTL clock generator. SYNC has a guaranteed 190kHz to 340kHz capture range.

300kHz operation optimizes the application circuit for component size and cost. 150kHz operation provides increased efficiency and improved load-transient response at low input-output voltage differences (see *Low-Voltage Operation* section).

#### Low-Noise Mode (SKIP Pin)

The low-noise mode ( $\overline{SKIP}$  = high) is useful for minimizing RF and audio interference in noise-sensitive applications such as Soundblaster<sup>™</sup> hi-fi audio-equipped systems, cellular phones, RF communicating computers, and electromagnetic pen-entry systems. See the summary of operating modes in Table 3.  $\overline{SKIP}$  can be driven from an external logic signal.

The MAX797 can reduce interference due to switching noise by ensuring a constant switching frequency regardless of load and line conditions, thus concentrating the emissions at a known frequency outside the system audio or IF bands. Choose an oscillator fre-

Soundblaster is a trademark of Creative Labs

quency where harmonics of the switching frequency don't overlap a sensitive frequency band. If necessary, synchronize the oscillator to a tight-tolerance external clock generator.

The low-noise mode ( $\overline{SKIP}$  = high) forces two changes upon the PWM controller. First, it ensures fixed-frequency operation by disabling the minimum-current comparator and ensuring that the PWM latch is set at the beginning of each cycle, even if the output is in regulation. Second, it ensures continuous inductor current flow, and thereby suppresses discontinuous-mode inductor ringing by changing the reverse current-limit detection threshold from zero to -100mV, allowing the inductor current to reverse at very light loads.

In most applications,  $\overline{\text{SKIP}}$  should be tied to GND in order to minimize quiescent supply current. Supply current with  $\overline{\text{SKIP}}$  high is typically 10mA to 20mA, depending on external MOSFET gate capacitance and switching losses.

Forced continuous conduction via  $\overline{\text{SKIP}}$  can improve cross regulation of transformer-coupled multiple-output supplies. This second function of the  $\overline{\text{SKIP}}$  pin produces a result that is similar to the method of adding secondary regulation via the SECFB feedback pin, but with much higher quiescent supply current. Still, improving cross regulation by enabling  $\overline{\text{SKIP}}$  instead of building in SECFB feedback can be useful in noisesensitive applications, since SECFB and  $\overline{\text{SKIP}}$  are mutually exclusive pins/functions in the MAX796 family.

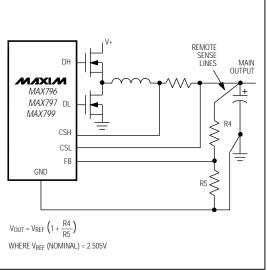

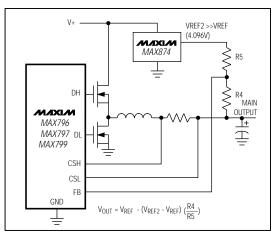

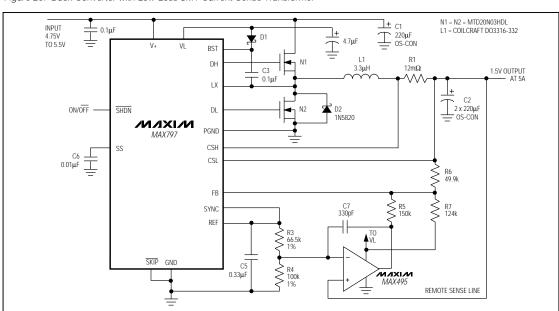

# Adjustable-Output Feedback (Dual-Mode FB Pin)

Adjusting the main output voltage with external resistors is easy for any of the devices in the MAX796 family, via the circuit of Figure 6. The nominal output voltage (given by the formula in Figure 6) should be set approximately 2% high in order to make up for the MAX796's -2.5% typical load-regulation error. For example, if designing for a 3.0V output, use a resistor ratio that results in a nominal output voltage of 3.06V. This slight offsetting gives the best possible accuracy. Recommended normal values for R5 range from  $5k\Omega$  to  $100k\Omega$ . To achieve a 2.505V nominal output, simply connect FB to CSL directly. To achieve output voltages lower than 2.5V, use an external reference-voltage source higher than VREF, as shown in Figure 7. For best accuracy, this second reference voltage should be much higher than VREF. Alternatively, an external op amp could be used to gain-up REF in order to create the second reference source. This scheme requires a minimum load on the output in order to sink the R3/R4 divider current.

Remote sensing of the output voltage, while not possible in fixed-output mode due to the combined nature of the voltage- and current-sense input (CSL), is easy to achieve in adjustable mode by using the top of the external resistor divider as the remote sense point. Fixed-output accuracy is guaranteed to be  $\pm 4\%$  over all conditions. In special circumstances, it may be necessary to improve upon this output accuracy. The High-Accuracy Adjustable-Output Application (Figure 18) provides  $\pm 2.5\%$  accuracy by adding an integrator-type error amplifier.

The breakdown voltage rating of the current-sense inputs (7V absolute maximum) determines the 6V maximum output adjustment range. To extend this output range, add two matched resistor dividers and speedup capacitors to form a level translator, as shown in Figure 8. Be sure to set these resistor ratios accurately (using 0.1% resistors), to avoid adding excessive error to the 100mV current-limit threshold.

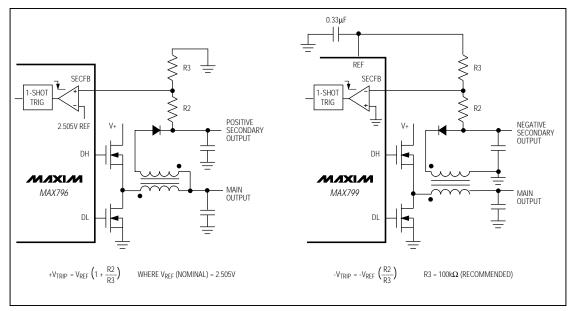

#### Secondary Feedback-Regulation Loop (SECFB Pin)

A flyback winding control loop regulates a secondary winding output (MAX796/MAX799 only), improving cross-regulation when the primary is lightly loaded or when there is a low input-output differential voltage. If SECFB crosses its regulation threshold (VREF for the

Figure 6. Adjusting the Main Output Voltage

Figure 7. Output Voltage Less than 2.5V

MAX796), a 1µs one-shot is triggered that extends the low-side switch's on-time beyond the point where the inductor current crosses zero (in discontinuous mode). This causes the inductor (primary) current to reverse, which in turn pulls current out of the output filter capacitor and causes the flyback transformer to operate in the forward mode. The low impedance presented by the transformer secondary in the forward mode dumps current into the secondary output, charging up the secondary capacitor and bringing SECFB back into regulation. The SECFB feedback loop does not improve secondary output accuracy in normal flyback mode, where the main (primary) output is heavily loaded. In this mode, secondary output accuracy is determined, as usual, by the secondary rectifier drop, turns ratio, and accuracy of the main output voltage. So, a linear post-regulator may still be needed in order to meet tight output accuracy specifications

The secondary output voltage-regulation point is determined by an external resistor divider at SECFB. For negative output voltages, the SECFB comparator is referenced to GND (MAX799); for positive output voltages, SECFB regulates at the 2.505V reference (MAX796). As a result, output resistor divider connections and design equations for the two device types differ slightly (Figure 9). Ordinarily, the secondary regulation point is set 5% to 10% below the voltage normally produced by the flyback effect. For example, if the output voltage as determined by the turns ratio is +15V, the feedback resistor ratio should be set to produce about +13.5V; otherwise, the SECFB one-shot might be triggered unintentionally, causing an unnecessary increase in supply current and output

Figure 8. Adjusting the Output Voltage to Greater than 6V

noise. In negative-output (MAX799) applications, the resistor divider acts as a load on the internal reference, which in turn can cause errors at the main output. Avoid overloading REF (see the Reference Load-Regulation Error vs. Load Current graph in the *Typical Operating Characteristics*).  $100\text{k}\Omega$  is a good value for R3 in MAX799 circuits.

#### Soft-Start Circuit (SS)

Soft-start allows a gradual increase of the internal current-limit level at start-up for the purpose of reducing input surge currents, and perhaps for power-supply sequencing. In shutdown mode, the soft-start circuit holds the SS capacitor discharged to ground. When SHDN goes high, a 4µA current source charges the SS capacitor up to 3.2V. The resulting linear ramp waveform causes the internal current-limit level to increase proportionally from 20mV to 100mV. The main output capacitor thus charges up relatively slowly, depending on the SS capacitor value. The exact time of the output rise depends on output capacitance and load current and is typically 1ms per nanofarad of soft-start capacitance. With no SS capacitor connected, maximum current limit is reached within 10µs.

#### Shutdown

Shutdown mode ( $\overline{SHDN}$  = 0V) reduces the V+ supply current to typically 1µA. In this mode, the reference and VL are inactive.  $\overline{SHDN}$  is a logic-level input, but it can be safely driven to the full V+ range. Connect  $\overline{SHDN}$  to V+ for automatic start-up. Do not allow slow transitions (slower than 0.02V/µs) on  $\overline{SHDN}$ .

#### Design Procedure

The five pre-designed standard application circuits (Figure 1 and Table 1) contain ready-to-use solutions for common applications. Use the following design procedure to optimize the basic schematic for different voltage or current requirements. Before beginning a design, firmly establish the following:

**VIN(MAX), the maximum input (battery) voltage.** This value should include the worst-case conditions, such as no-load operation when a battery charger or AC adapter is connected but no battery is installed. VIN(MAX) must not exceed 30V. This 30V upper limit is determined by the breakdown voltage of the BST floating gate driver to GND (36V absolute maximum).

VIN(MIN), the minimum input (battery) voltage. This should be taken at full-load under the lowest battery conditions. If VIN(MIN) is less than 4.5V, a special circuit must be used to externally hold up VL above 4.8V. If the minimum input-output difference is less than 1.5V, the filter capacitance required to maintain good AC load regulation increases.

#### Inductor Value

The exact inductor value isn't critical and can be adjusted freely in order to make tradeoffs among size, cost, and efficiency. Although lower inductor values will minimize size and cost, they will also reduce efficiency due to higher peak currents. To permit use of the physically smallest inductor, lower the inductance until the circuit is operating at the border between continuous and discontinuous modes. Reducing the inductor value even further, below this crossover point, results in discontinuous-conduction operation even at full load. This helps reduce output filter capacitance requirements but causes the core energy storage requirements to increase again. On the other hand, higher inductor values will increase efficiency, but at some point resistive losses due to extra turns of wire will exceed the benefit gained from lower AC current levels. Also, high inductor values can affect load-transient response; see the VSAG equation in the Low-Voltage Operation section.

The following equations are given for continuous-conduction operation since the MAX796 is mainly intended for high-efficiency battery-powered applications. See Appendix A in Maxim's *Battery Management and DC-DC Converter Circuit Collection* for crossover point and discontinuous-mode equations. Discontinuous conduction doesn't affect normal idle-mode operation.

Figure 9. Secondary-Output Feedback Dividers, MAX796 vs. MAX799

Three key inductor parameters must be specified: inductance value (L), peak current (IpEAK), and DC resistance (RDC). The following equation includes a constant LIR, which is the ratio of inductor peak-topeak AC current to DC load current. A higher value of LIR allows smaller inductance, but results in higher losses and ripple. A good compromise between size and losses is found at a 30% ripple current to load current ratio (LIR = 0.3), which corresponds to a peak inductor current 1.15 times higher than the DC load current.

$$L = \frac{V_{OUT} (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} x f x I_{OUT} x LIR}$$

where:

f = switching frequency, normally 150kHz or 300kHz

I<sub>OUT</sub> = maximum DC load current LIR = ratio of AC to DC inductor current, typically 0.3

The peak inductor current at full load is 1.15 x  $I_{OUT}$  if the above equation is used; otherwise, the peak current can be calculated by:

$$I_{PEAK} = I_{LOAD} + \frac{V_{OUT} (V_{IN}(MAX) - V_{OUT})}{2 \times f \times L \times V_{IN}(MAX)}$$

The inductor's DC resistance is a key parameter for efficiency performance and must be ruthlessly minimized, preferably to less than  $25m\Omega$  at  $I_{OUT} = 3A$ . If a standard off-the-shelf inductor is not available, choose a core with an LI2 rating greater than L x IPEAK2 and wind it with the largest diameter wire that fits the winding area. For 300kHz applications, ferrite core material is strongly preferred; for 150kHz applications, Kool-mu (aluminum alloy) and even powdered iron can be acceptable. If light-load efficiency is unimportant (in desktop 5V-to-3V applications, for example) then lowpermeability iron-powder cores, such as the Micrometals type found in Pulse Engineering's 2.1µH PE-53680, may be acceptable even at 300kHz. For high-current applications, shielded core geometries (such as toroidal or pot core) help keep noise, EMI, and switching-waveform jitter low.

#### **Current-Sense Resistor Value**

The current-sense resistor value is calculated according to the worst-case-low current-limit threshold voltage (from the *Electrical Characteristics* table) and the peak inductor current. The continuous-mode peak inductor-current calculations that follow are also useful for sizing the switches and specifying the inductor-current saturation ratings. In order to simplify the calculation, I<sub>LOAD</sub>

may be used in place of  $I_{PEAK}$  if the inductor value has been set for LIR = 0.3 or less (high inductor values) and 300kHz operation is selected. Low-inductance resistors, such as surface-mount metal-film resistors, are preferred.

#### Input Capacitor Value

Place a small ceramic capacitor (0.1µF) between V+ and GND, close to the device. Also, connect a low-ESR bulk capacitor directly to the drain of the high-side MOSFET. Select the bulk input filter capacitor according to input ripple-current requirements and voltage rating, rather than capacitor value. Electrolytic capacitors that have low enough ESR to meet the ripple-current requirement invariably have more than adequate capacitance values. Aluminum-electrolytic capacitors such as Sanyo OS-CON or Nichicon PL are preferred over tantalum types, which could cause power-up surge-current failure, especially when connecting to robust AC adaptors or low-impedance batteries. RMS input ripple current is determined by the input voltage and load current, with the worst possible case occurring at  $V_{IN} = 2 \times V_{OUT}$ :

$$I_{RMS} = I_{LOAD} \times \frac{\sqrt{V_{OUT} (V_{IN} - V_{OUT})}}{V_{IN}}$$

$$I_{RMS} = I_{LOAD} / 2 \text{ when } V_{IN} \text{ is } 2 \times V_{OUT}$$

#### **Output Filter Capacitor Value**

The output filter capacitor values are generally determined by the ESR (effective series resistance) and voltage rating requirements rather than actual capacitance requirements for loop stability. In other words, the low-ESR electrolytic capacitor that meets the ESR requirement usually has more output capacitance than is required for AC stability. Use only specialized low-ESR capacitors intended for switching-regulator applications, such as AVX TPS, Sprague 595D, Sanyo OS-CON, or Nichicon PL series. To ensure stability, the capacitor must meet *both* minimum capacitance and maximum ESR values as given in the following equations:

$$C_F > \frac{V_{REF} (1 + V_{OUT} / V_{IN(MIN)})}{V_{OUT} \times R_{SENSE} \times f}$$

$$R_{ESR} < \frac{R_{SENSE} \times V_{OUT}}{V_{REF}}$$

(can be multiplied by 1.5, see note below)

These equations are "worst-case" with 45 degrees of phase margin to ensure jitter-free fixed-frequency operation and provide a nicely damped output response for zero to full-load step changes. Some cost-conscious designers may wish to bend these rules by using less expensive (lower quality) capacitors, particularly if the load lacks large step changes. This practice is tolerable, provided that some bench testing over temperature is done to verify acceptable noise and transient response.

There is no well-defined boundary between stable and unstable operation. As phase margin is reduced, the first symptom is a bit of timing jitter, which shows up as blurred edges in the switching waveforms where the scope won't quite sync up. Technically speaking, this (usually) harmless jitter is unstable operation, since the switching frequency is now non-constant. As the capacitor quality is reduced, the jitter becomes more pronounced and the load-transient output voltage waveform starts looking ragged at the edges. Eventually, the load-transient waveform has enough ringing on it that the peak noise levels exceed the allowable output voltage tolerance. Note that even with zero phase margin and gross instability present, the output voltage noise never gets much worse than IPEAK x RESR (under constant loads, at least).

Designers of RF communicators or other noise-sensitive analog equipment should be conservative and stick to the guidelines. Designers of notebook computers and similar commercial-temperature-range digital systems can multiply the RESR value by a factor of 1.5 without hurting stability or transient response.

The output voltage ripple is usually dominated by the ESR of the filter capacitor and can be approximated as IRIPPLE x RESR. There is also a capacitive term, so the full equation for ripple in the continuous mode is  $V_{NOISE(p-p)} = I_{RIPPLE} \times (R_{ESR} + 1 / (2 \times pi \times f \times C_F))$ . In idle mode, the inductor current becomes discontinuous with high peaks and widely spaced pulses, so the noise can actually be higher at light load compared to full load. In idle mode, the output ripple can be calculated as:

$$V_{NOISE(p-p)} = \frac{0.02 \times RESR}{RSENSE} + \frac{0.0003 \times L \times [1 / V_{OUT} + 1 / (V_{IN} - V_{OUT})]}{(RSENSE)^2 \times CF}$$

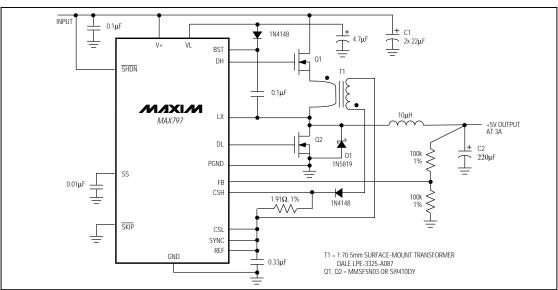

# Transformer Design (MAX796/MAX799 Only)

Buck-plus-flyback applications, sometimes called "coupled-inductor" topologies, need a transformer in order to generate multiple output voltages. The basic electrical design is a simple task of calculating turns ratios and adding the power delivered to the secondary in order to calculate the current-sense resistor and primary inductance. However, extremes of low input-output differentials, widely different output loading levels, and high turns ratios can complicate the design due to parasitic transformer parameters such as inter-winding capacitance, secondary resistance, and leakage inductance. For examples of what is possible with real-world transformers, see the graphs of Maximum Secondary Current vs. Input Voltage in the *Typical Operating Characteristics*.

Power from the main and secondary outputs is lumped together to obtain an equivalent current referred to the main output voltage (see Inductor L1 for definitions of parameters). Set the value of the current-sense resistor at 80mV / ITOTAL.

PTOTAL = the sum of the output power from all outputs

ITOTAL = PTOTAL / VOUT = the equivalent output current referred to VOUT

$$L(primary) = \frac{V_{OUT} (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times f \times I_{TOTAL} \times LIR}$$

$$Turns \ Ratio \ N = \frac{V_{SEC} + V_{FWD}}{V_{OUT(MIN)} + V_{RECT} + V_{SENSE}}$$

where: VSEC is the minimum required rectified secondary-output voltage

VFWD is the forward drop across the secondary rectifier

VouT(MIN) is the *minimum* value of the main output voltage (from the *Electrical Characteristics*)

VRECT is the on-state voltage drop across the synchronous-rectifier MOSFET

Vsense is the voltage drop across the sense

In positive-output (MAX796) applications, the transformer secondary return is often referred to the main output voltage rather than to ground in order to reduce the needed turns ratio. In this case, the main output voltage must first be subtracted from the secondary voltage to obtain VSEC.

### \_Selecting Other Components

#### **MOSFET Switches**

The two high-current N-channel MOSFETs must be logic-level types with guaranteed on-resistance specifications at VGS = 4.5V. Lower gate threshold specs are better (i.e., 2V max rather than 3V max). Drain-source breakdown voltage ratings must at least equal the maximum input voltage, preferably with a 20% derating factor. The best MOSFETs will have the lowest on-resistance per nanocoulomb of gate charge. Multiplying RDS(ON) x QG provides a meaningful figure by which to compare various MOSFETs. Newer MOSFET process technologies with dense cell structures generally give the best performance. The internal gate drivers can tolerate >100nC total gate charge, but 70nC is a more practical upper limit to maintain best switching times.

In high-current applications, MOSFET package power dissipation often becomes a dominant design factor. I<sup>2</sup>R power losses are the greatest heat contributor for both high- and low-side MOSFETs. I<sup>2</sup>R losses are distributed between Q1 and Q2 according to duty factor (see the equations below). Switching losses affect the upper MOSFET only, since the Schottky rectifier clamps the switching node before the synchronous rectifier turns on. Gate-charge losses are dissipated by the driver- er and don't heat the MOSFET. Ensure that both MOSFETs are within their maximum junction temperature at high ambient temperature by calculating the temperature rise according to package thermal-resistance specifications. The worst-case dissipation for the high-side MOSFET occurs at the minimum battery voltage, and the worst-case for the low-side MOSFET occurs at the maximum battery voltage.

PD (upper FET) =  $ILOAD^2 \times RDS(ON) \times DUTY$

+ V<sub>IN</sub> x I<sub>LOAD</sub> x f x

$$\left(\frac{\text{VIN x CRSS}}{\text{IGATE}} + 20\text{ns}\right)$$

PD (lower FET) =  $I_{LOAD}^2 \times R_{DS(ON)} \times (1 - DUTY)$ DUTY =  $(V_{OUT} + V_{O2}) / (V_{IN} - V_{O1})$

where: On-state voltage drop VQ\_ = ILOAD x RDS(ON)

CRSS = MOSFET reverse transfer capacitance

IGATE = DH driver peak output current capability

(1A typically)

20ns = DH driver inherent rise/fall time

Under output short circuit, the synchronous-rectifier MOSFET suffers extra stress and may need to be oversized if a continuous DC short circuit must be tolerated.

During short circuit, Q2's duty factor can increase to greater than 0.9 according to:

Q2 DUTY (short circuit) = 1 - [ $V_{Q2}$  / ( $V_{IN(MAX)}$  -  $V_{Q1}$ )] where the on-state voltage drop  $V_{Q}$  = (120mV / RSENSE) x RDS(ON).

#### **Rectifier Diode D1**

Rectifier D1 is a clamp that catches the negative inductor swing during the 110ns dead time between turning off the high-side MOSFET and turning on the low-side. D1 must be a Schottky type in order to prevent the lossy parasitic MOSFET body diode from conducting. It is acceptable to omit D1 and let the body diode clamp the negative inductor swing, but efficiency will drop one or two percent as a result. Use an MBR0530 (500mA rated) type for loads up to 1.5A, a 1N5819 type for loads up to 3A, or a 1N5822 type for loads up to 10A. D1's rated reverse breakdown voltage must be at least equal to the maximum input voltage, preferably with a 20% derating factor.

#### **Boost-Supply Diode D2**

A signal diode such as a 1N4148 works well for D2 in most applications. If the input voltage can go below 6V, use a small (20mA) Schottky diode for slightly improved efficiency and dropout characteristics. Don't use large power diodes such as 1N5817 or 1N4001, since high junction capacitance can cause VL to be pumped up to excessive voltages.

# Rectifier Diode D3 (Transformer Secondary Diode)

The secondary diode in coupled-inductor applications must withstand high flyback voltages greater than 60V, which usually rules out most Schottky rectifiers. Common silicon rectifiers such as the 1N4001 are also prohibited, as they are far too slow. This often makes fast silicon rectifiers such as the MURS120 the only choice. The flyback voltage across the rectifier is related to the VIN-VOUT difference according to the transformer turns ratio:

VFLYBACK = VSEC + (VIN - VOUT) x N

where: N is the transformer turns ratio SEC/PRI VSEC is the maximum secondary DC output voltage VOUT is the primary (main) output voltage

Subtract the main output voltage (Vout) from VFLYBACK in this equation if the secondary winding is returned to Vout and not to ground. The diode reverse breakdown rating must also accommodate any ringing due to leakage inductance. D3's current rating should be at least twice the DC load current on the secondary output.

#### Low-Voltage Operation

Low input voltages and low input-output differential voltages each require some extra care in the design. Low absolute input voltages can cause the VL linear regulator to enter dropout, and eventually shut itself off. Low input voltages relative to the output (low VIN-VOUT differential) can cause bad load regulation in multi-output flyback applications. See the design equations in the *Transformer Design* section. Finally, low VIN-VOUT differentials can also cause the output voltage to sag when the load current changes abruptly. The amplitude of the sag is a function of inductor value and maximum duty factor (an *Electrical Characteristics* parameter, 93% guaranteed over temperature at f = 150kHz) as follows:

$$V_{SAG} = \frac{(I_{STEP})^2 \times L}{2 \times C_F \times (V_{IN(MIN)} \times D_{MAX} - V_{OUT})}$$

The cure for low-voltage sag is to increase the value of the output capacitor. For example, at  $V_{IN}=5.5V$ ,  $V_{OUT}=5V$ ,  $L=10\mu H$ , f=150kHz, a total capacitance of  $660\mu F$  will prevent excessive sag. Note that only the capacitance requirement is increased and the ESR requirements don't change. Therefore, the added capacitance can be supplied by a low-cost bulk capacitor in parallel with the normal low-ESR capacitor.

### \_Applications Information

#### Heavy-Load Efficiency Considerations

The major efficiency loss mechanisms under loads are, in the usual order of importance:

- P(I2R), I2R losses

- P(gate), gate-charge losses

- P(diode), diode-conduction losses

- · P(tran), transition losses

- · P(cap), capacitor ESR losses

- P(IC), losses due to the operating supply current of the IC

Inductor-core losses are fairly low at heavy loads because the inductor's AC current component is small. Therefore, they aren't accounted for in this analysis. Ferrite cores are preferred, especially at 300kHz, but powdered cores such as Kool-mu can work well.

$P(I^2R) = (I_{LOAD})^2 \times (R_{DC} + R_{DS}(ON) + R_{SENSE})$

where R<sub>DC</sub> is the DC resistance of the coil, R<sub>DS</sub>(ON) is the MOSFET on-resistance, and R<sub>SENSE</sub> is the current-

#### **Table 4. Low-Voltage Troubleshooting**

| SYMPTOM                                                                                                   | CONDITION                                                                                                                      | ROOT CAUSE                                                                                                                              | SOLUTION                                                                                                          |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|