# General Description

The MAX191 is a monolithic, CMOS, 12-bit analog-todigital converter (ADC) featuring differential inputs, track/hold (T/H), internal voltage reference, internal or external clock, and parallel or serial  $\mu$ P interface. The MAX191 has a 7.5 $\mu$ s conversion time, a 2 $\mu$ s acquisition time, and a guaranteed 100ksps sample rate.

The MAX191 operates from a single +5V supply or from dual ±5V supplies, allowing ground-referenced bipolar input signals. The device features a logic power-down input, which reduces the 3mA V<sub>DD</sub> supply current to 50 $\mu$ A max, including the internal-reference current.

Decoupling capacitors are the only external components needed for the power supply and reference. This ADC operates with either an external reference, or an internal reference that features an adjustment input for trimming system gain errors.

The MAX191 provides three interface modes: two 8-bit parallel modes, and a serial interface mode that is compatible with SPI<sup>TM</sup>, QSPI<sup>TM</sup>, and Microwire<sup>TM</sup> serial-interface standards.

Applications Battery-Powered Data Logging PC Pen Digitizers High-Accuracy Process Control Electromechanical Systems Data-Acquisition Boards for PCs Automatic Testing Systems Telecommunications Digital Signal Processing (DSP)

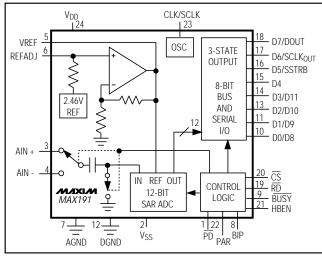

# Functional Diagram

\_Features

- 12-Bit Resolution, 1/2LSB Linearity

- + +5V or ±5V Operation

- Built-In Track/Hold

- Internal Reference with Adjustment Capability

- Low Power: 3mA Operating Mode 20µA Power-Down Mode

- 100ksps Tested Sampling Rate

- ♦ Serial and 8-Bit Parallel µP Interface

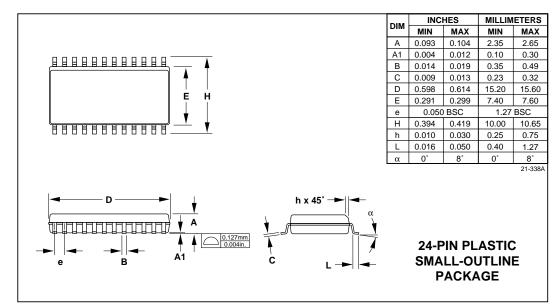

- + 24-Pin Narrow DIP and Wide SO Packages

### \_Ordering Information

| PART       | TEMP. RANGE     | PIN-PACKAGE           | ERROR<br>(LSBs) |

|------------|-----------------|-----------------------|-----------------|

| MAX191ACNG | 0°C to +70°C    | 24 Narrow Plastic DIP | ±1/2            |

| MAX191BCNG | 0°C to +70°C    | 24 Narrow Plastic DIP | ±1              |

| MAX191ACWG | 0°C to +70°C    | 24 Wide SO            | ±1/2            |

| MAX191BCWG | 0°C to +70°C    | 24 Wide SO            | ±1              |

| MAX191BC/D | 0°C to +70°C    | Dice*                 | ±1              |

| MAX191AENG | -40°C to +85°C  | 24 Narrow Plastic DIP | ±1/2            |

| MAX191BENG | -40°C to +85°C  | 24 Narrow Plastic DIP | ±1              |

| MAX191AEWG | -40°C to +85°C  | 24 Wide SO            | ±1/2            |

| MAX191BEWG | -40°C to +85°C  | 24 Wide SO            | ±1              |

| MAX191AMRG | -55°C to +125°C | 24 Narrow CERDIP**    | ±1/2            |

| MAX191BMRG | -55°C to +125°C | 24 Narrow CERDIP**    | ±1              |

\* Dice are specified at  $T_A = +25^{\circ}$ C, DC parameters only. \*\* Contact factory for availability and processing to MIL-STD-883.

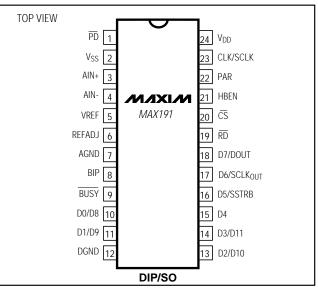

## Pin Configuration

TM SPI and QSPI are trademarks of Motorola. Microwire is a trademark of National Semiconductor.

MINXI/M

\_\_\_\_\_\_M

Call toll free 1-800-998-8800 for free samples or literature.

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to DGND0.3V to +7V<br>V <sub>SS</sub> to AGND7V to +0.3V        |

|---------------------------------------------------------------------------------|

| V <sub>DD</sub> to V <sub>SS</sub>                                              |

| AGND, VREF, REFADJ to DGND0.3V to (V <sub>DD</sub> + 0.3V)                      |

| AIN+, AIN-, $\overline{PD}$ to V <sub>SS</sub> 0.3V to (V <sub>DD</sub> + 0.3V) |

| CS, RD, CLK, BIP, HBEN, PAR, to DGND0.3V to (V <sub>DD</sub> + 0.3V)            |

| <b>BUSY</b> , D0-D7 to DGND0.3V to (V <sub>DD</sub> + 0.3V)                     |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                           |

| Narrow Plastic DIP (derate 13.33mW/°C above +70°C)1067mW                        |

| Wide SO (derate 11.76mW/°C above +70°C)941mW                                    |

| Narrow CERDIP (derate 12.50mW/°C above +70°C)1000mW                             |

Operating Temperature Ranges:

| MAX191_C                             | 0°C to +70°C    |

|--------------------------------------|-----------------|

| MAX191_E                             |                 |

| MAX191_M                             | -55°C to +125°C |

| Storage Temperature Range            | 65°C to +160°C  |

| Lead Temperature (soldering, 10sec). | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 5V \pm 5\%, V_{SS} = 0V \text{ or } -5V \pm 5\%, f_{CLK} = 1.6MHz, 50\% \text{ duty cycle, AIN-} = AGND, BIP = 0V, slow-memory mode, internal-reference mode, reference compensation mode-external, synchronous operation, Figure 6, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                             | SYMBOL            | CONDITIONS                              | MIN      | TYP  | MAX   | UNITS  |

|-------------------------------------------------------|-------------------|-----------------------------------------|----------|------|-------|--------|

| DC ACCURACY (Note 2)                                  | 4                 |                                         | <b>I</b> |      |       |        |

| Resolution                                            |                   |                                         | 12       |      |       | Bits   |

| Integral Nonlinearity                                 | INL               | MAX191A                                 |          |      | ±1/2  | LSB    |

| integral Nonlinearity                                 | INL               | MAX191B                                 |          |      | ±1    | LSD    |

| Differential Nonlinearity                             | DNL               | No missing codes over temperature       |          |      | ±1    | LSB    |

| Offset Error                                          |                   | MAX191A                                 |          |      | ±1    | LSB    |

| Oliset Elloi                                          |                   | MAX191B                                 |          |      | ±2    | LSD    |

|                                                       |                   | MAX191A                                 |          |      | ±2    |        |

| Gain Error (Note 3)                                   |                   | MAX191B                                 |          |      | ±3    | LSB    |

| Gain-Error Tempco (Note 4)                            |                   | Excludes internal-reference drift       |          | ±0.2 |       | ppm/°C |

| DYNAMIC ACCURACY (sample r                            | ate = 100kHz      | $V_{\rm IN} = 4V_{\rm p-p}$             |          |      |       | 1      |

| Signal-to-Noise plus Distortion<br>Ratio              | SINAD             | 1kHz input signal, $T_A = +25^{\circ}C$ | 70       |      |       | dB     |

| Total Harmonic Distortion<br>(up to the 5th Harmonic) | THD               | 1kHz input signal, $T_A = +25^{\circ}C$ |          |      | -80   | dB     |

| Spurious-Free Dynamic Range                           | SFDR              | 1kHz input signal, $T_A = +25^{\circ}C$ | 80       |      |       | dB     |

| CONVERSION RATE                                       |                   |                                         |          |      |       | 1      |

| Conversion Time (Note 5)                              | +                 | Synchronous CLK (12 to 13 CLKs)         | 7.50     |      | 8.125 |        |

| Conversion Time (Note 5)                              | t <sub>CONV</sub> | Internal CLK, CL = 120pF                | 6        | 12   | 18    | μs     |

| Track/Hold Acquisition Time                           |                   |                                         |          |      | 2     | μs     |

| Aperture Delay                                        |                   |                                         |          | 25   |       | ns     |

| Aperture Jitter                                       |                   |                                         |          | 50   |       | ps     |

| External Clock Frequency<br>Range (Note 6)            | f <sub>CLK</sub>  |                                         | 0.1      |      | 1.6   | MHz    |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 5V \pm 5\%, V_{SS} = 0V \text{ or } -5V \pm 5\%, f_{CLK} = 1.6MHz, 50\% \text{ duty cycle, AIN-} = AGND, BIP = 0V, slow-memory mode, internal-reference mode, reference compensation mode-external, synchronous operation, Figure 6, T_A = T_{MIN}$  to T<sub>MAX</sub>, unless otherwise noted.) (Note 1)

| PARAMETER                                        | SYMBOL           | CONDITIONS                                        | MIN             | TYP   | MAX      | UNITS  |

|--------------------------------------------------|------------------|---------------------------------------------------|-----------------|-------|----------|--------|

| ANALOG INPUT                                     |                  |                                                   | •               |       |          |        |

| Input Voltage Range (Note 7)                     |                  |                                                   | V <sub>SS</sub> |       | $V_{DD}$ | V      |

| Input Leakage Current                            |                  | $V_{IN} = V_{SS}$ to $V_{DD}$                     |                 |       | ±10      | μΑ     |

| Input Capacitance (Note 6)                       |                  |                                                   |                 | 45    | 80       | pF     |

| Small-Signal Bandwidth                           |                  |                                                   |                 | 2     |          | MHz    |

| INTERNAL REFERENCE                               |                  |                                                   |                 |       |          |        |

| VREF Output Voltage                              |                  | $T_A = +25^{\circ}C$                              | 4.076           | 4.096 | 4.116    | V      |

|                                                  |                  | MAX191_C                                          |                 |       | 50       |        |

| VREF Output Tempco (Note 8)                      |                  | MAX191_E                                          |                 |       | 60       | ppm/°0 |

|                                                  |                  | MAX191_M                                          |                 |       | 80       |        |

| Output Current Capability (Note 9)               |                  | $T_A = +25^{\circ}C$                              |                 |       | 2        | mA     |

| Load Regulation                                  |                  | $T_A = +25^{\circ}C$ , $I_{OUT} = 0mA$ to 2mA     |                 |       | 4        | mV     |

| Output Short-Circuit Current                     |                  |                                                   |                 | 18    |          | mA     |

| Capacitive Load Required                         |                  | Reference compensation mode-external              | 4.7             |       |          | μF     |

| Power-Supply Rejection                           |                  | $V_{DD} = \pm 5\%, V_{SS} = \pm 5\%$              |                 | ±300  |          | μV     |

| REFADJ Input Adjustment Range<br>(Note 10)       |                  |                                                   | -60             |       | 30       | mV     |

| REFADJ Disable Threshold                         |                  |                                                   | 4.5             |       |          | V      |

| REFADJ Output Voltage                            |                  |                                                   |                 | 2.4   |          | V      |

| REFADJ Input Current                             |                  | REFADJ = 5V                                       |                 |       | 60       | μA     |

|                                                  |                  |                                                   |                 |       |          |        |

| Input Voltage Range                              |                  | External-reference mode                           | 2.5             |       | 5.0      | V      |

| Input Current                                    |                  | External-reference = 5V                           |                 |       | 1        | mA     |

| Input Resistance                                 |                  | External-reference mode                           | 5               | 10    |          | kΩ     |

| LOGIC INPUTS                                     |                  |                                                   |                 |       |          |        |

| Input Low Voltage                                | V <sub>IL</sub>  | CS, RD, CLK, HBEN, PAR, BIP                       |                 |       | 0.8      | V      |

| Input High Voltage                               | V <sub>IH</sub>  | CS, RD, CLK, HBEN, PAR, BIP                       | 2.4             |       |          | V      |

| Input Current                                    | I <sub>IN</sub>  | $V_{IN} = 0V \text{ to } V_{DD}$                  |                 |       | ±10      | μA     |

|                                                  | 1                | $\overline{PD}$ = high/float                      |                 |       | ±200     |        |

| Input Current CLK                                | I <sub>IN</sub>  | PD = Iow                                          |                 | ±0.1  |          | μA     |

| Input Capacitance (Note 6)                       | C <sub>IN</sub>  |                                                   |                 |       | 10       | pF     |

| PD Input Low Voltage                             | V <sub>IL</sub>  |                                                   |                 |       | 0.5      | V      |

| PD Input High Voltage                            | V <sub>IH</sub>  |                                                   | 4.5             |       |          | V      |

| PD Input Current                                 | I <sub>IN</sub>  | $\overline{PD}$ = 0V to V <sub>DD</sub> (Note 11) |                 |       | ±20      | μA     |

| PD External Leakage for Float<br>State (Note 12) |                  | Maximum current allowed for "floating state"      |                 |       | ±100     | nA     |

| PD Floating-State Voltage                        | V <sub>FLT</sub> | Reference compensation mode-external              |                 | 2.8   |          | V      |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 5V \pm 5\%, V_{SS} = 0V \text{ or } -5V \pm 5\%, f_{CLK} = 1.6MHz, 50\% \text{ duty cycle, AIN-} = AGND, BIP = 0V, slow-memory mode, internal-reference mode, reference compensation mode-external, synchronous operation, Figure 6, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                  | SYMBOL          | COND                                                  | MIN                          | TYP   | MAX | UNITS |     |

|--------------------------------------------|-----------------|-------------------------------------------------------|------------------------------|-------|-----|-------|-----|

| LOGIC OUTPUTS                              |                 |                                                       |                              |       |     |       | 1   |

| Output Low Voltage                         | Vol             | I <sub>OUT</sub> = 1.6mA                              |                              |       |     | 0.4   | V   |

| Output High Voltage                        | VOH             | I <sub>OUT</sub> = -200μA                             |                              | 4.0   |     |       | V   |

| Three-State Leakage Current                | ١L              | D0/D8-D7/DOUT                                         |                              |       |     | ±10   | μA  |

| Three-State Output<br>Capacitance (Note 6) | Cout            |                                                       |                              |       |     | 15    | pF  |

| POWER REQUIREMENTS                         |                 |                                                       |                              |       |     |       | 1   |

| Positive Supply Voltage                    | V <sub>DD</sub> |                                                       |                              | 4.75  |     | 5.25  | V   |

| Negative Supply Voltage                    | Vss             |                                                       |                              | -5.25 |     | 0     | V   |

| Desitive Supply Current                    | 100             | $\overline{CS} = \overline{RD} = V_{DD}$ ,            | $\overline{PD}$ = high/float |       | 3   | 5     | mA  |

| Positive Supply Current                    | IDD             | AIN = 5V, D0/D8-                                      | $\overline{PD} = IOW$        |       | 20  | 50    | μA  |

| Negative Supply Current                    | lee             | D7/DOUT = 0V or<br>VDD, HBEN = PAR                    | $\overline{PD}$ = high/float |       | 20  | 100   |     |

| Negative Supply Current                    | Iss             | $=$ BIP = 0V or V <sub>DD</sub> $\overline{PD}$ = low |                              |       | 1   | 20    | μA  |

| Positive Supply Rejection (Note 13)        |                 | FS change, $V_{DD} = 5V \pm 5\%$                      |                              |       |     | ±1/2  | LSB |

| Negative Supply Rejection (Note 13)        |                 | FS change, Vss = $-5V \pm 5\%$                        |                              |       |     | ±1/2  | LSB |

# **TIMING CHARACTERISTICS (see Figures 6-10)**

(V\_DD =5V  $\pm 5\%,$  V\_SS = 0V or -5V  $\pm 5\%,$  T\_A = T\_MIN to T\_MAX, unless otherwise noted.) (Note 14)

| PARAMETER                                  | SYMBOL | CONDITIONS    | T <sub>A</sub> = +2<br>MIN TYP | 5°C<br>MAX | MAX1<br>MIN TY | 91C/E<br>(P MAX | M<br>MIN | AX191M<br>TYP MAX | UNITS |

|--------------------------------------------|--------|---------------|--------------------------------|------------|----------------|-----------------|----------|-------------------|-------|

| CS to RD Setup Time                        | t1     |               | 0                              |            | 0              |                 | 0        |                   | ns    |

| RD to BUSY Delay                           | t2     | $C_L = 50 pF$ |                                | 120        |                | 140             |          | 160               | ns    |

| Data Access Time (Note 15)                 | t3     | CL = 100pF    |                                | 120        |                | 140             |          | 160               | ns    |

| RD Pulse Width                             | t4     |               | 150                            |            | 150            |                 | 150      |                   | ns    |

| CS to RD Hold Time                         | t5     |               | 0                              |            | 0              |                 | 0        |                   | ns    |

| Data Setup Time After<br>BUSY (Note 15)    | t6     |               |                                | 80         |                | 100             |          | 120               | ns    |

| Bus-Relinquish Time (Note 16)              | t7     |               |                                | 100        |                | 110             |          | 120               | ns    |

| HBEN to RD Setup Time                      | t8     |               | 80                             |            | 100            |                 | 120      |                   | ns    |

| HBEN to RD Hold Time                       | t9     |               | 0                              |            | 0              |                 | 0        |                   | ns    |

| Delay Between Read<br>Operations (Note 6)  | t10    |               | 200                            |            | 200            |                 | 200      |                   | ns    |

| Delay Between Conversions                  | t11    |               | 2                              |            | 2              |                 | 2        |                   | μs    |

| Aperture Delay                             | t12    | Jitter < 50ps | 25                             |            |                |                 |          |                   | ns    |

| CLK to BUSY Delay (Note 6)                 | t13    |               |                                | 200        |                | 230             |          | 260               | ns    |

| SCLK <sub>OUT</sub> to SSTRB<br>Rise Delay | t14    |               |                                | 100        |                | 130             |          | 150               | ns    |

| SCLK <sub>OUT</sub> to SSTRB<br>Fall Delay | t15    |               |                                | 100        |                | 130             |          | 150               | ns    |

# TIMING CHARACTERISTICS (see Figures 6-10) (continued)

$(V_{DD} = 5V \pm 5\%, V_{SS} = 0V \text{ or } -5V \pm 5\%, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.})$  (Note 14)

| PARAMETER                         | SYMBOL          | CONDITIONS | T <sub>A</sub> = +25°C<br>MIN TYP MAX | MAX191C/E<br>MIN TYP MAX | MAX191M<br>MIN TYP MAX | UNITS |

|-----------------------------------|-----------------|------------|---------------------------------------|--------------------------|------------------------|-------|

| CS or RD Hold Time                | t16             |            | 10                                    | 10                       | 10                     | ns    |

| CS or RD Setup Time               | t17             |            | 150                                   | 150                      | 150                    | ns    |

| CS to DOUT Three-State            | t19             |            | 100                                   | 110                      | 120                    | ns    |

| SCLK to SCLKOUT Delay             | t20             |            | 160                                   | 180                      | 200                    | ns    |

| SCLK <sub>OUT</sub> to DOUT Delay | t <sub>21</sub> |            | 100                                   | 130                      | 150                    | ns    |

| SCLK to DOUT Delay                | t22             |            | 240                                   | 260                      | 280                    | ns    |

| SCLK to SSTRB Delay               | t23             |            | 260                                   | 310                      | 350                    | ns    |

Note 1: Performance at power-supply tolerance limits guaranteed by power-supply rejection test.

Note 2:  $V_{DD} = 5V$ ,  $V_{SS} = 0V$ , FS = VREF.

**Note 3:** FS = VREF, offset nulled, ideal last-code transition = FS - 3/2 LSB.

**Note 4:** Gain-Error Tempco =  $\Delta$ GE is the gain-error change from T<sub>A</sub> = +25°C to T<sub>MIN</sub> or T<sub>MAX</sub>.

Note 5: Conversion time defined as the number of clock cycles times the clock period; clock has a 50% duty cycle.

**Note 6:** Guaranteed by design, not production tested.

Note 7: AIN+, AIN- must not exceed supplies for specified accuracy.

**Note 8:** VREF TC =  $\Delta$ T, where  $\Delta$ VREF is reference-voltage change from T<sub>A</sub> = +25°C to T<sub>MIN</sub> or T<sub>MAX</sub>.

**Note 9:** Output current should not change during conversion. This current is in addition to the current required by the internal DAC.

**Note 10:** REFADJ adjustment range is defined as the allowed voltage excursion on REFADJ relative to its unadjusted value of 2.4V. This will typically result in a 1.7 times larger change in the REF output (Figure 19a).

Note 11: This current is included in the PD supply current specification.

**Note 12:** Floating the  $\overline{PD}$  pin guarantees external compensation mode.

**Note 13:** VREF = 4.096V, external reference.

**Note 14:** All input control signals are specified with  $t_r = t_f = 5ns$  (10% to 90% of 5V) and timed from a voltage level of 1.6V.

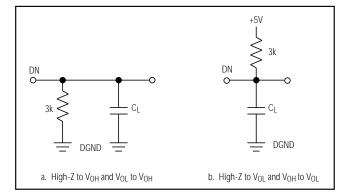

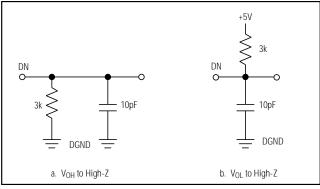

Note 15: t<sub>3</sub> and t<sub>6</sub> are measured with the load circuits of Figure 1 and defined as the time required for an output to cross 0.8V or 2.4V.

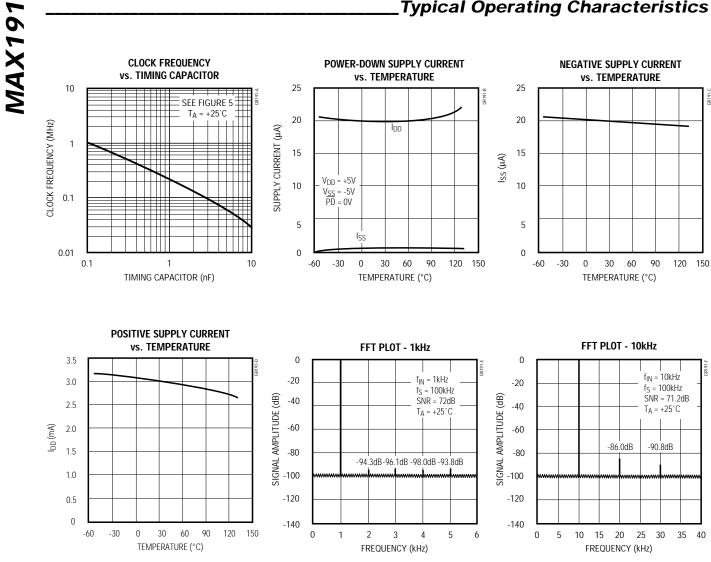

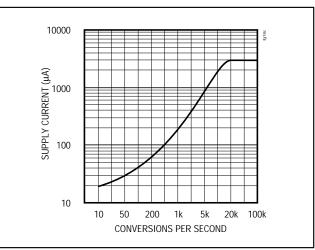

**Typical Operating Characteristics**

# \_Pin Description

| PIN | NAME                   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PD                     | Power-Down Input. A logic low at PD deactivates the ADC - only the bandgap reference is active. A logic high selects normal operation, internal-reference compensation mode. An open-circuit condition selects normal operation, external-reference compensation mode.                                                                                                                                           |

| 2   | V <sub>SS</sub>        | Negative Supply, 0V to -5.25V                                                                                                                                                                                                                                                                                                                                                                                    |

| 3   | AIN+                   | Sampled Analog Input                                                                                                                                                                                                                                                                                                                                                                                             |

| 4   | AIN-                   | Analog Input Return. Pseudo-differential (see Gain and Offset Adjustment section).                                                                                                                                                                                                                                                                                                                               |

| 5   | VREF                   | Reference-Buffer Output for Internal Reference. Input for external reference when REFADJ is connected to $V_{\text{DD}}$ .                                                                                                                                                                                                                                                                                       |

| 6   | REFADJ                 | Reference Adjust. Connect to V <sub>DD</sub> to use an extended reference at VREF.                                                                                                                                                                                                                                                                                                                               |

| 7   | AGND                   | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8   | BIP                    | BIP = low selects unipolar mode,<br>BIP = high selects bipolar mode (see <i>Gain and Offset Adjustment</i> section)                                                                                                                                                                                                                                                                                              |

| 9   | BUSY                   | BUSY Output is low during a conversion.                                                                                                                                                                                                                                                                                                                                                                          |

| 10  | D0/D8                  | Three-State Data Outputs: LSB = D0                                                                                                                                                                                                                                                                                                                                                                               |

| 11  | D1/D9                  | Three-State Data Outputs                                                                                                                                                                                                                                                                                                                                                                                         |

| 12  | DGND                   | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                   |

| 13  | D2/D10                 | Three-State Data Outputs                                                                                                                                                                                                                                                                                                                                                                                         |

| 14  | D3/D11                 | Three-State Data Outputs: MSB = D11                                                                                                                                                                                                                                                                                                                                                                              |

| 15  | D4                     | Three-State Data Output                                                                                                                                                                                                                                                                                                                                                                                          |

| 16  | D5/SSTRB               | Three-State Data Output/Serial Strobe Output in serial mode                                                                                                                                                                                                                                                                                                                                                      |

| 17  | D6/SCLK <sub>OUT</sub> | Three-State Data Output/Serial Clock Output in serial mode                                                                                                                                                                                                                                                                                                                                                       |

| 18  | D7/DOUT                | Three-State Data Output/Data Output in serial mode                                                                                                                                                                                                                                                                                                                                                               |

| 19  | RD                     | Read Input. In parallel mode, a low signal starts a conversion when $\overline{CS}$ and HBEN are low (memory mode). RD also enables the outputs when $\overline{CS}$ is low. In serial mode, $\overline{RD}$ = low enables SCLK <sub>OUT</sub> and SSTRB when CS is low. $\overline{RD}$ = high forces SCLK <sub>OUT</sub> and SSTRB into a high-impedance state.                                                |

| 20  | CS                     | Chip-Select Input must be low for the ADC to recognize $\overline{RD}$ and HBEN inputs in parallel mode. The falling edge of $\overline{CS}$ starts a conversion in serial mode. $\overline{CS}$ = high in serial mode forces SCLK <sub>OUT</sub> , SSTRB, and DOUT into a high-impedance state.                                                                                                                 |

| 21  | HBEN                   | High-Byte Enable Input. In parallel mode, HBEN = high multiplexes the 4 MSBs of the conversion result into the lower bit outputs. HBEN = high also disables conversion starts. HBEN = low places the 8 LSBs onto the data bus. In serial mode, HBEN = low enables $SCLK_{OUT}$ to operate during the conversion only, HBEN = high enables $SCLK_{OUT}$ to operate continuously, provided $\overline{CS}$ is low. |

| 22  | PAR                    | Sets the output mode. PAR = high selects parallel output mode. PAR = low selects serial output mode.                                                                                                                                                                                                                                                                                                             |

| 23  | CLK/SCLK               | Clock Input/Serial Clock Input in serial mode. An external TTL-/CMOS-compatible clock may be applied to this pin, or a capacitor (120pF nominal) may be connected between CLK and DGND to operate the internal oscillator.                                                                                                                                                                                       |

| 24  | Vdd                    | Positive Supply, +5V ±5%                                                                                                                                                                                                                                                                                                                                                                                         |

Figure 1. Load Circuits for Access Time

MAX191

Figure 2. Load Circuits for Bus-Relinquish Time

# **Detailed Description**

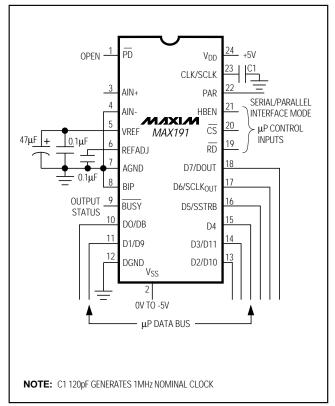

The MAX191 uses successive approximation and input track/hold (T/H) circuitry to convert an analog input signal to a 12-bit digital output. Flexible control logic provides easy interface to microprocessors ( $\mu$ Ps), so most applications require only the addition of passive components. No external hold capacitor is required for the T/H. Figure 3 shows the MAX191 in its simplest operational configuration.

### **Pseudo-Differential Input**

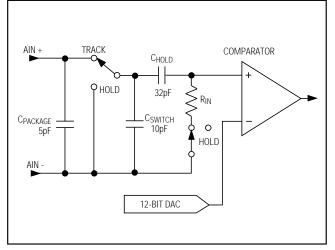

The sampling architecture of the ADC's analog comparator is illustrated in the Equivalent Input Circuit (Figure 4). A capacitor switching between the AIN+ and AIN- inputs acquires the signal at the ADC's analog input. At the end of the conversion, the capacitor reconnects to AIN+ and charges to the input signal. An external input buffer is usually not needed for lowbandwidth input signals (<100Hz) because the ADC disconnects from the input during the conversion. In

Figure 3. Operational Diagram

unbuffered applications, an input filter capacitor reduces conversion noise, but also may limit input bandwidth.

When converting a single-ended input signal, AINshould be connected to AGND. If a differential signal is connected, consider that the configuration is pseudo differential – only the signal side to the input channel is held by the T/H. The return side (AIN-) must remain stable within  $\pm 0.5$ LSB ( $\pm 0.1$ LSB for best results) with respect to AGND during a conversion. Accomplish this by connecting a  $0.1\mu$ F capacitor from AIN- to AGND.

### Analog Input – Track/Hold

The T/H enters its tracking mode when the ADC is deselected ( $\overline{CS}$  pin is held high and  $\overline{BUSY}$  pin is high). Hold mode starts approximately 25ns after a conversion is initiated. The variation in this delay from one conversion to the next (aperture jitter) is about 50ps. Figures 6-10 detail the T/H and interface timing for the various interface modes.

Figure 4. Equivalent Input Circuit

The time required for the T/H to acquire an input signal is a function of how quickly its input capacitance is charged. If the input signal's source impedance is high, the acquisition time lengthens and more time must be allowed between conversions. Acquisition time is calculated by:  $t_{ACQ} = 10(R_S + R_{IN})C_{HOLD}$  (but never less than 2µs), where  $R_{IN} = 2k\Omega$ ,  $R_S =$  source impedance of the input signal, and  $C_{HOLD} = 32pF$  (see Figure 4).

#### Input Bandwidth

The ADC's input tracking circuitry has a 1MHz typical large-signal bandwidth characteristic, and a 30V/µs slew rate. It is possible to digitize high-speed transients and measure periodic signals with bandwidths exceeding the ADC's sample rate of 100ksps by using undersampling techniques. Note that if undersampling is used to measure high-frequency signals, special care must be taken to avoid aliasing errors. Without adequate input bandpass filtering, out-of-band signals and noise may be aliased into the measurement band.

#### **Input Protection**

Internal protection diodes, which clamp the analog input to V<sub>DD</sub> and V<sub>SS</sub>, allow AIN+ to swing from (V<sub>SS</sub> - 0.3V) to (V<sub>DD</sub> + 0.3V) with no risk of damage to the ADC. However, for accurate conversions near full scale, AIN+ should not exceed the power supplies by more than 50mV because ADC accuracy is affected when the protection diodes are even slightly forward biased.

Figure 5. Internal Clock Circuit

### \_Digital Interface

#### Starting a Conversion

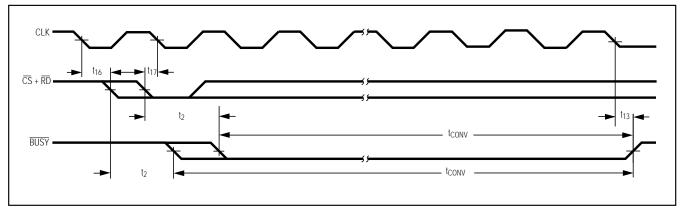

In parallel mode, the ADC is controlled by the  $\overline{CS}$ ,  $\overline{RD}$ , and HBEN inputs, as shown in Figure 6. The T/H enters hold mode and a conversion starts at the falling edge of  $\overline{CS}$  and  $\overline{RD}$  while HBEN (not shown) is low. **BUSY** goes low as soon as the conversion starts. On the falling edge of the 13th input clock pulse after the conversion starts, **BUSY** goes high and the conversion result is latched into three-state output buffers. In serial mode, the falling edge of  $\overline{CS}$  initiates a conversion, and the T/H enters hold mode. Data is shifted out serially as the conversion proceeds (Figure 10). See the *Parallel Digital-Interface Mode* and *Serial-Interface Mode* sections for details.

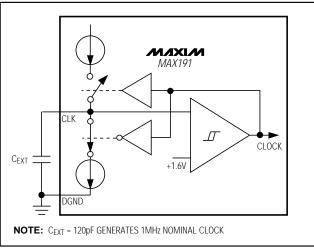

#### Internal/External Clock

Figure 5 shows the MAX191 clock circuitry. The ADC includes internal circuitry to generate a clock with an external capacitor. As indicated in the *Typical Operating Characteristics*, a 120pF capacitor connected between the CLK and DGND pins generates a 1MHz nominal clock frequency (Figure 5).

Alternatively, an external clock (between 100kHz and 1.6MHz) can be applied to CLK. When using an external clock source, acceptable clock duty cycles are between 45% and 55%.

MAX191

Figure 6. CS, RD, and CLK Synchronous Operation

### **Clock and Control Synchronization**

For best analog performance on the MAX191, the clock should be synchronized to the conversion start signals ( $\overline{CS}$  and  $\overline{RD}$ ) as shown in Figure 6. A conversion should not be started in the 50ns before a clock edge nor in the 100ns after it. This ensures that CLK transitions are not coupled to the analog input and sampled by the T/H. The magnitude of this feedthrough can be a few millivolts. When the clock and conversion start signals are synchronized, small end-point errors (offset and full-scale) are the most that can be generated by clock feedthrough. Even these errors (which can be trimmed out) can be avoided by ensuring that the start of a conversion ( $\overline{RD}$  or  $\overline{CS}$  falling edge) does not occur close to a clock transition (Figure 6), as described above.

### Parallel Digital-Interface Mode

#### Output-Data Format

The data output from the MAX191 is straight binary in the unipolar mode. In the bipolar mode, the MSB is inverted (see Figure 22). The 12 data bits can be output either in two 8-bit bytes or as a serial output. Table 1 shows the data-bus output format.

A 2-byte read uses outputs D7-D0. Byte selection is controlled by HBEN. When HBEN is low, the lower 8 bits appear at the data outputs. When HBEN is high, the upper 4 bits appear at D0-D3 with the leading 4 bits low in locations D4-D7.

#### **Timing and Control**

Conversion-start and data-read operations are controlled by the HBEN,  $\overline{CS}$ , and  $\overline{RD}$  digital inputs. A logic low is required on all three inputs to start a conversion, and once the conversion is in progress it cannot be restarted.  $\overline{BUSY}$  remains low during the entire conversion cycle. The timing diagrams of Figures 7-10 outline two parallel-interface modes and one serial mode.

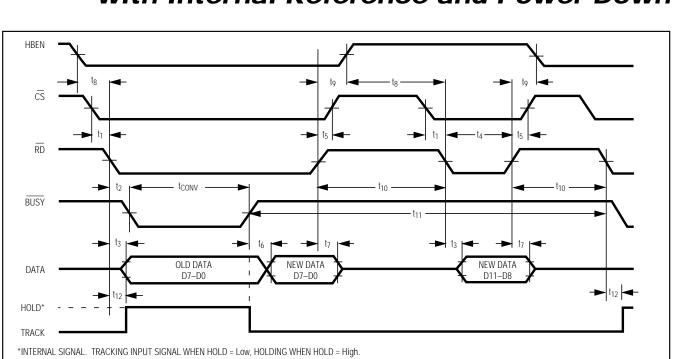

#### Slow-Memory Mode

In slow-memory mode, the device appears to the  $\mu$ P as a slow peripheral or memory. Conversion is initiated with a read instruction (see Figure 7 and Table 2). Set the PAR pin high for parallel interface mode. Beginning with HBEN low, taking  $\overline{CS}$  and  $\overline{RD}$  low starts the conversion. The analog input is sampled on the falling edge of  $\overline{RD}$ . BUSY remains low while the conversion is in progress. The previous conversion result appears at the digital outputs until the end of conversion, when BUSY returns high. The output latches are then updated with the newest results of the 8 LSBs on D7-D0. A second read operation with HBEN high places the 4 MSBs, with 4 leading 0s, on data outputs D7-D0. The second read operation does not start a new conversion because HBEN is high.

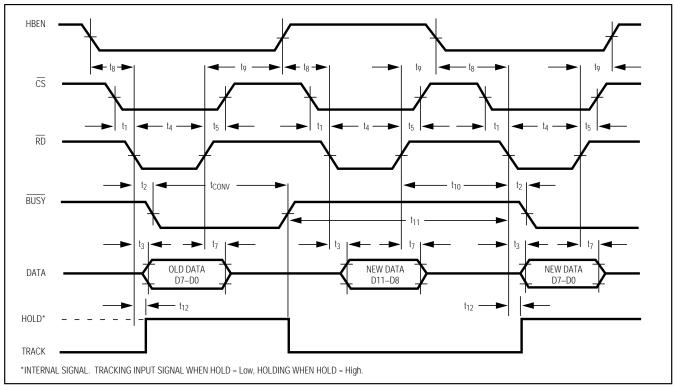

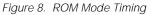

#### **ROM Mode**

As in slow-memory mode, D7-D0 are used for 2-byte reads. A conversion starts with a read instruction with HBEN and  $\overline{CS}$  low. The T/H samples the input on the falling edge of  $\overline{RD}$  (see Figure 8 and Table 3). PAR is set high. At this point the data outputs contain the 8 LSBs from the previous conversion. Two more read operations are needed to access the conversion result. The first occurs with HBEN high, where the 4 MSBs with 4 leading 0s are accessed. The second read, with HBEN low, outputs the 8 LSBs and also starts a new conversion.

Figure 9 and Table 4 show how to read output data within one conversion cycle without starting another conversion. Trigger the falling edge of a read on the rising edge of the first clock cycle after conversion end (when  $\overline{\text{BUSY}}$  goes high). As mentioned previously, two more read operations (after  $\overline{\text{BUSY}}$  goes high) are need-

Figure 7. Slow-Memory Mode Timing

**MAX191**

Figure 9. ROM Mode Timing, Reading Data without Starting a Conversion

Figure 10. Serial-Interface Mode Timing Diagram (RD = low)

## Table 1. Data-Bus Output, $\overline{CS} = \overline{RD} = Low$

| PIN NAME                                               | D7/DOUT | D6/SCLK <sub>OUT</sub> | D5/SSTRB         | D4  | D3/D11 | D2/D10 | D1/D9 | D0/D8 |

|--------------------------------------------------------|---------|------------------------|------------------|-----|--------|--------|-------|-------|

| HBEN = 0, PAR = 1,<br>PARALLEL MODE                    | D7      | D6                     | D5               | D4  | D3     | D2     | D1    | D0    |

| HBEN = 1, PAR = 1,<br>PARALLEL MODE                    | Low     | Low                    | Low              | Low | D11    | D10    | D9    | D8    |

| HBEN = X, PAR = 0,<br>SERIAL MODE, $\overline{RD} = 0$ | DOUT    | SCLKOUT                | SSTRB            | Low | Low    | Low    | Low   | Low   |

| HBEN = X, PAR = 0,<br>SERIAL MODE, $\overline{RD}$ = 1 | DOUT    | Three-<br>Stated       | Three-<br>Stated | Low | Low    | Low    | Low   | Low   |

Note: D7/DOUT – D0/D8 are the ADC data output pins.

D11 – D0 are the 12-bit conversion results. D11 is the MSB.

DOUT = Three-state data output. Data output in serial mode.

$\mathsf{SCLK}_\mathsf{OUT}$  = Three-state data output. Clock output in serial mode.

SSTRB = Three-state data output. Strobe output in serial mode.

### Table 2. Slow-Memory Mode, 2-Byte Read Data-Bus Status

| PIN NAME               | D7/DOUT | D6/SCLK <sub>OUT</sub> | D5/SSTRB | D4  | D3/D11 | D2/D10 | D1/D9 | D0/D8 |

|------------------------|---------|------------------------|----------|-----|--------|--------|-------|-------|

| FIRST READ (New Data)  | D7      | D6                     | D5       | D4  | D3     | D2     | D1    | D0    |

| SECOND READ (New Data) | Low     | Low                    | Low      | Low | D11    | D10    | D9    | D8    |

## Table 3. ROM Mode, 2-Byte Read Data-Bus Status

| PIN NAME               | D7/DOUT | D6/SCLK <sub>OUT</sub> | D5/SSTRB | D4  | D3/D11 | D2/D10 | D1/D9 | D0/D8 |

|------------------------|---------|------------------------|----------|-----|--------|--------|-------|-------|

| FIRST READ (Old Data)  | D7      | D6                     | D5       | D4  | D3     | D2     | D1    | D0    |

| SECOND READ (New Data) | Low     | Low                    | Low      | Low | D11    | D10    | D9    | D8    |

| THIRD READ (New Data)  | D7      | D6                     | D5       | D4  | D3     | D2     | D1    | D0    |

### Table 4. ROM Mode, 2-Byte Read Data-Bus Status without Starting a Conversion Cycle

| PIN NAME               | D7/DOUT | D6/SCLKOUT | D5/SSTRB | D4  | D3/D11 | D2/D10 | D1/D9 | D0/D8 |

|------------------------|---------|------------|----------|-----|--------|--------|-------|-------|

| FIRST READ (Old Data)  | D7      | D6         | D5       | D4  | D3     | D2     | D1    | D0    |

| SECOND READ (New Data) | D7      | D6         | D5       | D4  | D3     | D2     | D1    | D0    |

| THIRD READ (New Data)  | Low     | Low        | Low      | Low | D11    | D10    | D9    | D8    |

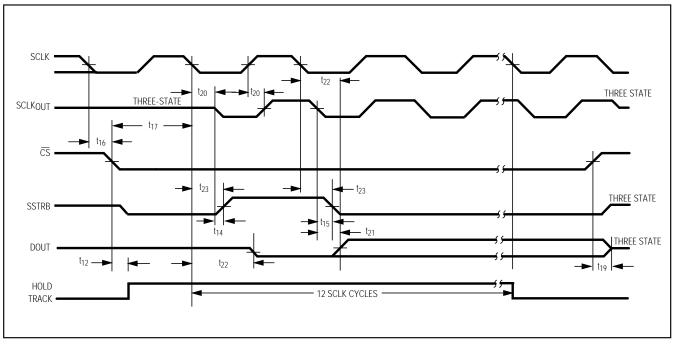

Figure 11. Simple Serial-to-Parallel Interface

ed to access the conversion results. The only difference is that now the low byte can be read first. This happens by allowing the first read operation to occur with HBEN low, where the 8 LSBs are accessed. The second read, with HBEN high, accesses the 4 MSBs with 4 leading 0s.

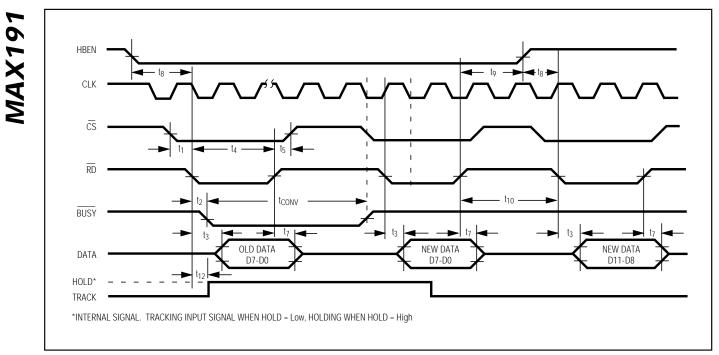

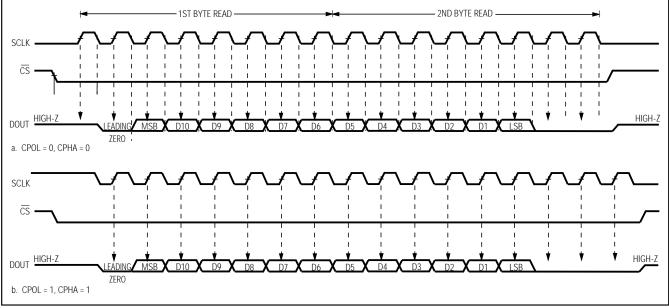

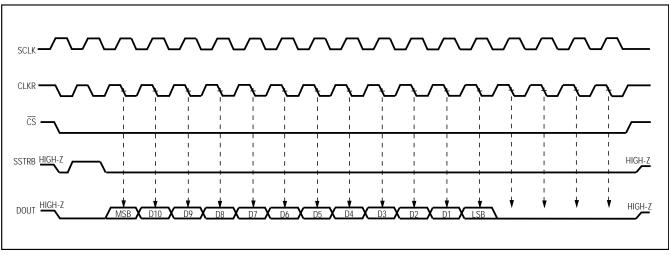

#### Serial-Interface Mode

The serial mode is compatible with Microwire, SPI and QSPI serial interfaces. In addition, a framing signal (SSTRB) is provided that allows the devices to interface with the TMS320 family of DSPs. Set PAR low for serial mode. A falling edge on  $\overline{CS}$  causes the T/H to sample the input (Figure 10). Conversion always begins on the next falling edge of SCLK, regardless of where CS occurs. The DOUT line remains high-impedance until a conversion begins. During the MSB decision, DOUT remains low (leading 0), while SSTRB goes high to indicate that a data frame is beginning. The data is available at DOUT on the rising edge of SCLK (SCLKOUT when using an internal clock) and transitions on the falling edge. DOUT remains low after all data bits have been shifted out, inserting trailing 0s in the data stream until CS returns high. The SCLK<sub>OUT</sub> signal is synchronous with the internal or external clock.

For interface flexibility, DOUT, SCLK<sub>OUT</sub> and SSTRB signals enter a high-impedance state when  $\overline{CS}$  is high. When  $\overline{CS}$  is low,  $\overline{RD}$  controls the status of SCLK<sub>OUT</sub> and SSTRB outputs. A logic low  $\overline{RD}$  enables SCLK<sub>OUT</sub> and SSTRB, while a logic high forces both outputs into a high-impedance state. Also, with  $\overline{CS}$  low and HBEN high, SCLK<sub>OUT</sub> drives continuously, regardless of conversion status. This is useful with µPs that require a continuous serial clock. If  $\overline{CS}$  and HBEN are low, SCLK<sub>OUT</sub> is output only during the conversion cycle, while the converter internal clock runs continuously.

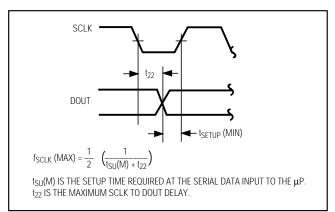

Figure 12.  $f_{SCLK}(MAX)$  is limited by the setup time required by the serial data input to the  $\mu P$ .

This is useful for creating a simple serial-to-parallel interface without shift-register overflow (Figure 11).

#### Maximum Clock Rate in Serial Mode

The maximum SCLK rate depends on the minimum setup time required at the serial data input to the  $\mu$ P and the ADC's DOUT to SCLK delay (t<sub>22</sub>) (see Figure 12). The maximum f<sub>SCLK</sub> is as follows:

$$f_{SCLK}(MAX) = (1/2) \times 1/(t_{SU}(M) + t_{22})$$

where  $t_{su}(M)$  is the minimum data-setup time required at the serial data input to the  $\mu P.$  For example,

Figure 13. Common Serial-Interface Connections to the MAX191

Motorola's MC68HC11A8 data book specifies a 100ns minimum data-setup time. Using the worst case for a military grade part of  $t_{22}$  = 280ns (see *Timing Characteristics*) and substituting in the above equation indicates a maximum SCLK frequency of 1.3MHz.

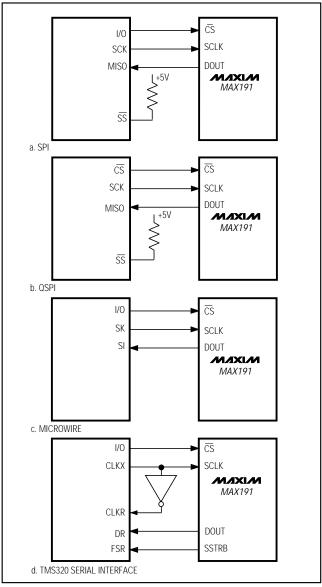

### Using the MAX191 with SPI, QSPI and Microwire Serial Interfaces

Figure 13 shows interface connections to the MAX191 for common serial-interface standards.

#### SPI and Microwire (CPOL=0, CPHA=0)

The MAX191 is compatible with SPI, QSPI and Microwire serial-interface standards. When using SPI or QSPI, two modes are available to interface with the MAX191. You can set CPOL = 0 and CPHA = 0 (Figure 14a), or set CPOL = 1 and CPHA = 1 (Figure 14b). When using CPOL = 0 and CPHA = 0, the conversion begins on the first falling edge of SCLK following  $\overline{CS}$  going low. Data is available from DOUT on the rising edge of SCLK, and transitions on the falling edge. Two consecutive 1-byte reads are required to get the full 12 bits from the ADC. The first byte contains the following, in this order: a leading unknown bit (DOUT will still be high-impedance on the first bit), a 0, and the six MSBs. The second byte contains the remaining six LSBs and two trailing 0s.

#### SPI (CPOL=1, CPHA=1)

Setting CPOL = 1 and CPHA = 1 starts the clock high during a read instruction. The MAX191 will shift out a

leading 0 followed by the 12 data bits and three trailing 0s (Figure 14b).

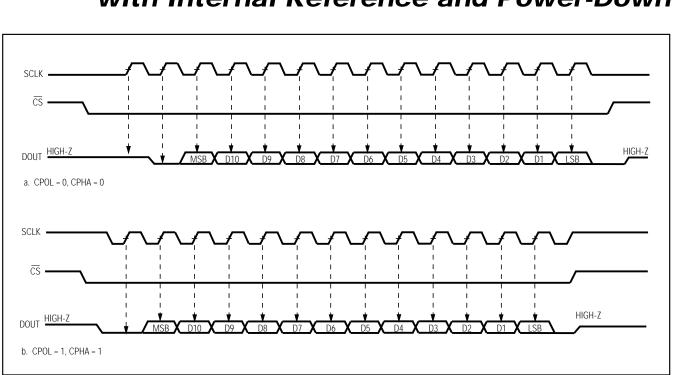

#### QSPI

Unlike SPI, which requires two 1-byte reads to acquire the 12 bits of data from the ADC, QSPI allows the minimum number of clock cycles required to clock in the data (Figure 15).

#### TMS320 Serial Interface

Figure 13d shows the pin connections to interface the MAX191 to the TMS320. Since the MAX191 makes data available on the rising edge of SCLK and the TMS320 shifts data in on the falling edge of CLKR, use CLKX of the DSP to drive SCLK, and **CLKX** to drive the DSP's CLKR input. The inverter's propagation delay also provides more data-setup time at the DSP. For example, with no inverter delay, and using  $t_{22} = 280$ ns and  $f_{SCLK} = 1.6$ MHz, the available setup time before the SCLK transition is:

setup time =  $1/(2 \times f_{SCLK}) - t_{22} = 1/(2 \times 1.6E6) - 280ns = 32ns$ This still exceeds the 13ns minimum DR setup time before the CLKR goes low (tsu(DR)), however, a generic 74HC04 provides an additional 20ns setup time (see Figure 13d).

Figure 16 shows the DSP interface timing characteristics. The DSP begins clocking data in on the falling edge of CLKR after the falling edge of SSTRB. Following the data transfer, the DSP receive shift register (RSR) contains a 16-bit word consisting of the 12 data bits, MSB first, followed by four trailing 0s.

Figure 14. SPI/Microwire Serial-Interface Timing

Low-Power, 12-Bit Sampling ADC with Internal Reference and Power-Down

Figure 15. QSPI Serial-Interface Timing

Figure 16. TMS320 Interface Timing

**MAX191**

### Applications Information

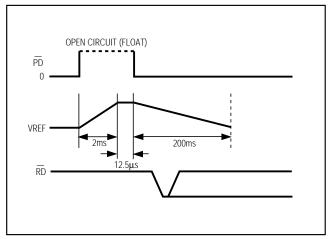

### Power-Down Mode/Initialization After Power-Up

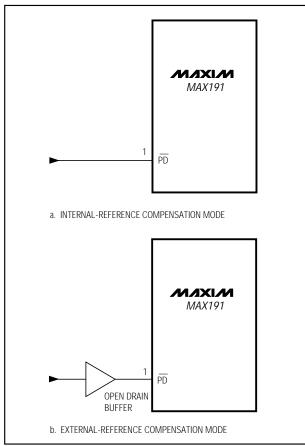

In some battery-powered systems, it is desirable to power down or remove power from the ADC during inactive periods. To power down the MAX191, drive PD low. In this mode, all internal ADC circuitry is off except the reference, and the ADC consumes less than 50 $\mu$ A max (assuming all signals  $\overline{CS}$ ,  $\overline{RD}$ , CLK, and HBEN are static and within 200mV of the supplies). To initialize the MAX191 at power-up, perform a single conversion and disregard the data outputs. Figure 17 shows a practical way to drive the PD pin. If using internal reference compensation, drive PD between VDD and DGND with a µP I/O pin or other logic device (Figure 17a). For external-reference compensation mode, use the circuit in Figure 17b to drive PD between DGND and the floating voltage of PD. An alternative is to drive PD with three-state logic or a switch, provided the off leakage does not exceed 100nA.

Figure 17. Drive Circuits for  $\overline{PD}$  pin

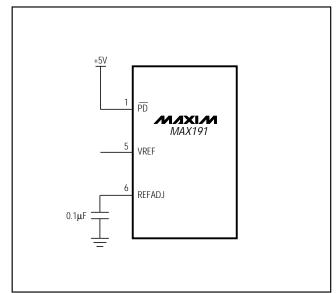

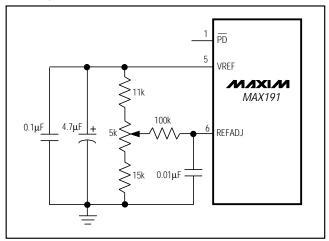

### Internal Reference

The internal 4.096V reference is available at VREF and must be bypassed to AGND with a 4.7 $\mu$ F low-ESR capacitor (less than 1/2 $\Omega$ ) in parallel with a 0.1 $\mu$ F capacitor, unless internal-reference compensation mode is used (see the *Internal Reference Compensation* section). This minimizes noise and maintains a low reference impedance at high frequencies. The reference output can be disabled by connecting REFADJ to VDD when using an external reference.

#### **Reference-Compensation Modes**

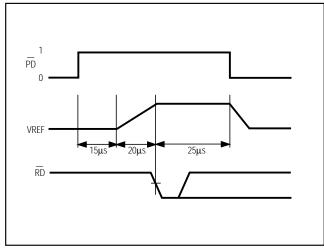

Power-down performance can be optimized for a given conversion rate by selecting either internal or external reference compensation.

#### Internal Compensation

The connection for internal compensation is shown in Figure 18a. In this mode, the reference stabilizes quickly enough so that a conversion typically starts within 35µs after the ADC is reactivated (**PD** pulled high). In this compensation mode, the reference buffer requires longer recovery time from SAR transients, therefore requiring a slower clock (and conversion time). With internal reference compensation, the typical conversion time rises to 25µs (Figure 18b). Figure 18c illustrates the typical average supply current vs. conversion rate, which can be achieved using power-down between conversions.

Figure 18a. Internal-Compensation Mode Circuit

Figure 18b. Low Average-Power Mode Operation (Internal Compensation)

#### External Compensation

Figure 19a shows the connection for external compensation with reference adjustment. In this mode, an external  $4.7\mu$ F capacitor compensates the reference output amplifier, allowing for maximum conversion speed and lowest conversion noise. However, when reactivating the ADC after power-down, the reference takes typically 2ms to fully charge the  $4.7\mu$ F capacitor, so more time is required before a conversion can start (Figure 19b). Thus, the average current consumed in power-up/powerdown operations is higher in external compensation mode than in internal compensation mode.

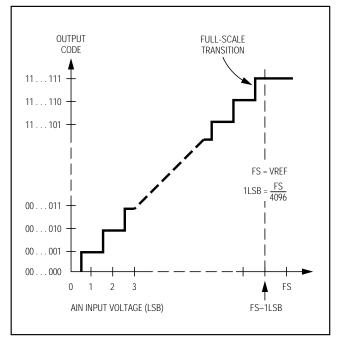

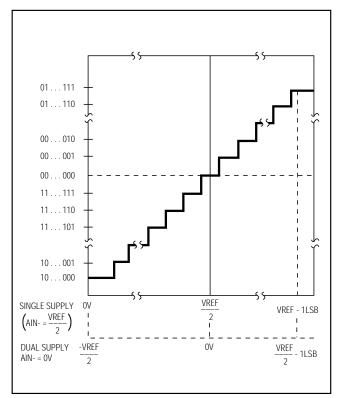

#### Gain and Offset Adjustment

Figure 20 depicts the nominal, unipolar input/output (I/O) transfer function, and Figure 22 shows the bipolar I/O transfer function. Code transitions occur halfway between successive integer LSB values. Note that 1LSB = 1.00mV (4.096V/4096) for unipolar operation and 1LSB = 1.00mV ((4.096V/2 - -4.096V/2)/4096) for bipolar operation.

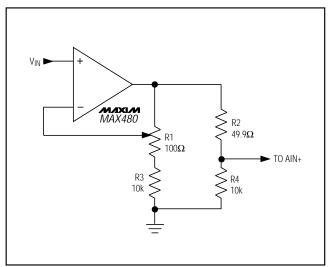

Figures 19a and 21a show how to adjust the ADC gain in applications that require full-scale range adjustment. The connection shown in Figure 21a provides  $\pm 0.5\%$ for  $\pm 20$ LSBs of adjustment range and is recommended for applications that use an external reference. On the other hand, Figure 19a is recommended for applications that use the internal reference, because it uses fewer external components.

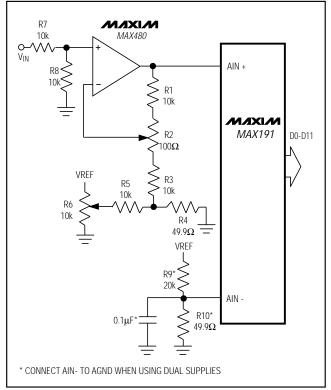

If both offset and full scale need adjustment, the circuit in Figure 21b is recommended. For single-supply ADCs, it is virtually impossible to null system negative offset errors. However, the MAX191 input configuration is pseudo-differential – only the difference in volt-

Figure 19a. External-Compensation Mode with Internal Reference Adjustment Circuit

age between AIN+ and AIN- will be converted into its digital representation. By applying a small positive voltage to AIN-, the 0 input voltage at AIN+ can be adjusted to above or below AIN- voltage, thus nulling positive or negative system offset errors. R9 and R10 can be removed for applications that require only positive system errors to be nulled. To trim the offset error of the MAX191, apply 1/2LSB to the analog input and adjust R6 so the digital output code changes between 000 (hex) and 001 (hex). To adjust full scale, apply FS - 1 1/2LSBs and adjust R2 until the output code changes between FFE (hex) and FFF (hex). Because interaction occurs between adjustments, offset should be adjusted before gain. For an input gain of two, remove R7 and R8.

# **MAX191**

Figure 19b. Low Average-Power Mode Operation (External Compensation)

The MAX191 accepts input voltages from AGND to VDD while operating from a single supply, and Vss to VDD when operating from dual supplies. Figure 22 shows the bipolar input transfer function with AIN- connected to midscale for single-supply operation and connected to GND operating from dual supplies. When operating from a single supply, the MAX191 can be configured for bipolar operation on its pseudo-differential input. Instead of using AIN- as an analog input return, AINcan be set to a different positive potential voltage above ground (BIP pin is set high). The sampled analog input (AIN+) can swing to any positive voltage above and below AIN-, and the ADC performs bipolar conversions with respect to AIN-. When operating from dual supplies, the MAX191 full-scale range is from -VREF/2 to +VREF/2.

#### **Digital Bus Noise**

If the data bus connected to the ADC is active during a conversion, crosstalk from the data pins to the ADC comparator may generate errors. Slow-memory mode avoids this problem by placing the  $\mu$ P in a wait state during the conversion. In ROM mode, if the data bus is active during the conversion, it should be isolated from the ADC using three-state drivers.

The ADC generates considerable digital noise in ROM mode when  $\overline{RD}$  or  $\overline{CS}$  go high and the output data drivers are disabled after a conversion has started. This noise can cause large errors if it occurs when the SAR latches a comparator decision. To avoid this problem,  $\overline{RD}$  and  $\overline{CS}$  should be active for less than one clock cycle. If this is not possible,  $\overline{RD}$  or  $\overline{CS}$  should go high at the rising edge of CLK, since the comparator output is always latched on falling edges of CLK.

Figure 20. Unipolar Transfer Function

Figure 21a. Trim Circuit for Gain  $(\pm 0.5\%)$

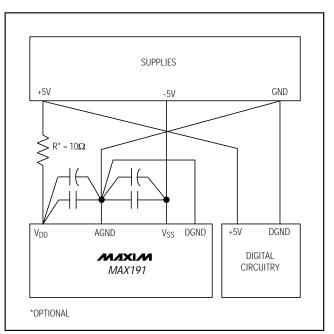

### Layout, Grounding, Bypassing

Use printed circuit boards for best system performance. Wire-wrap boards are not recommended. Board layout should ensure that digital- and analog-signal lines are separated from each other. Do not run analog and digital (especially clock) lines parallel to one another, or digital lines underneath the ADC package.

Figure 21b. Offset (±10mV) and Gain (±1%) Trim Circuit

Figure 23 shows the recommended system ground connections. Establish a single-point ground ("star" ground point) at AGND, separate from the logic ground. Connect all other analog grounds and DGND to it. No other digital-system ground should be connected to this single-point analog ground. The ground return to the power supply for this star ground should be low impedance and as short as possible for noise-free operation.

High-frequency noise in the V<sub>DD</sub> power supply may affect the high-speed comparator in the ADC. Bypass these supplies to the single-point analog ground with 0.01µF and 10µF bypass capacitors. Minimize capacitor lead lengths for best supply-noise rejection. If the +5V power supply is very noisy, a 10 $\Omega$  resistor can be connected as a lowpass filter to filter out supply noise (Figure 23).

Figure 22. Bipolar Transfer Function

Figure 23. Power-Supply Grounding Connection

### \_Dynamic Performance

High-speed sampling capability and throughput make the MAX191 ideal for wideband signal processing. To support these and other related applications, Fast Fourier Transform (FFT) test techniques guarantee the ADC's dynamic frequency response, distortion, and noise at the rated throughput. Specifically, this involves applying a low-distortion sine wave to the ADC input and recording the digital conversion results for a specified time. The data is then analyzed using an FFT algorithm, which determines its spectral content. Conversion errors are then seen as spectral elements outside the fundamental input frequency. FFT plots are shown in the *Typical Operating Characteristics*.

ADCs have traditionally been evaluated by specifications such as zero and full-scale error, integral nonlinearity (INL), and differential nonlinearity (DNL). Such parameters are widely accepted for specifying performance with DC and slowly varying signals, but are less useful in signal-processing applications where the ADC's impact on the system transfer function is the main concern. The significance of various DC errors does not translate well to the dynamic case, so different tests are required.

Signal-to-Noise Ratio (SNR) is the ratio between the RMS amplitude of the fundamental input frequency to the RMS amplitude of all other A/D output signals, except signal harmonics. Signal-to-Noise + Distortion ratio (SINAD) is the same as the SNR, but includes signal harmonics.

The theoretical minimum A/D noise is caused by quantization error and is a direct result of the ADC's resolution: SNR = (6.02n + 1.76) dB, where n is the number of bits of resolution. 74dB is the SNR of a perfect 12-bit ADC.

By transposing the equation that converts resolution to SNR we can compute the effective resolution or the "effective number of bits" the ADC provides from the measured SNR:

### n = (SNR - 1.76)/6.02

### **Total Harmonic Distortion**

Total Harmonic Distortion (THD) is the ratio of the RMS sum of all harmonics of the input signal (in the frequency band above DC and below one-half the sample rate) to the fundamental itself. This expressed as:

THD = 20log

$$\left[ \sqrt{(V_2^2 + V_3^2 + V_4^2 + V_5^2 + ... + V_n^2)} / V_1 \right]$$

where  $V_1$  is the fundamental RMS amplitude and  $V_2$  to  $V_n$  are the amplitudes of the 2nd through n<sup>th</sup> harmonics.

### Spurious-Free Dynamic Range

Spurious-free dynamic range is the ratio of the fundamental RMS amplitude to the amplitude of the next largest spectral component (in the frequency band above DC and below one-half the sample rate). Usually this peak occurs at some harmonic of the input frequency. But if the ADC is exceptionally linear, it can occur at a random peak in the ADC's noise floor.

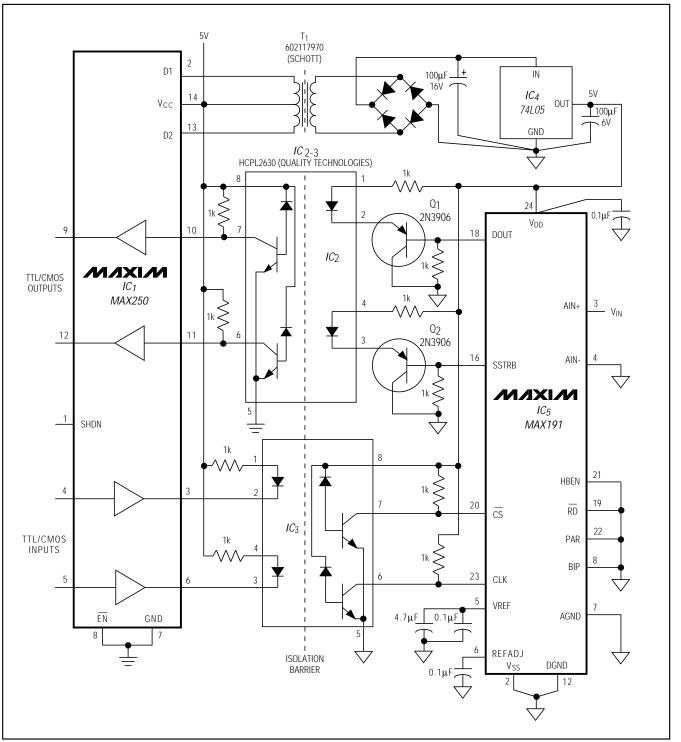

### **Opto-Isolated A/D Interface**

Many industrial applications require isolation to prevent excessive current flow where ground disparities exist between the ADC and the rest of the system. In Figure 24, a MAX250 and four 6N136 opto-couplers create an isolation barrier between the MAX191 and  $\mu$ P.

The 6N136 opto-couplers limit the maximum data rate to 90kbps. This requires a slower clock, and therefore a longer conversion time.

Figure 24. Isolated Data-Acquisition Circuit

**MAX191**

# Package Information