# **Product Family Specification**

SCA3000 Series 3-axis accelerometer

## **TABLE OF CONTENTS**

| General Description                                         | 5  |

|-------------------------------------------------------------|----|

| 1.1 Introduction                                            | 5  |

| 1.2 Functional Description                                  | 5  |

| 1.2.1 Sensing element                                       |    |

| 1.2.2 Interface IC                                          |    |

| 1.2.3 Factory calibration                                   |    |

| 1.2.4 Supported features                                    |    |

| 1.2.5 Operation modes                                       |    |

| 1.2.5.1 Measurement                                         |    |

| 1.2.5.2 Motion Detection                                    | 6  |

| 1.2.6 Free-Fall Detection                                   | 6  |

| 1.2.7 Interrupt                                             | 7  |

| 1.2.8 Temperature output                                    |    |

| 1.2.9 Output ring buffer                                    | 7  |

| Reset and power up, Operation Modes, HW functions and Clock | 7  |

| 2.1 Reset and power up                                      | 7  |

| 2.2 Measurement Mode                                        | 7  |

| 2.2.1 Description                                           |    |

| 2.2.1.1 Bypass measurement mode                             |    |

| 2.2.1.2 Narrow band measurement mode                        |    |

| 2.2.2 Usage                                                 |    |

| 2.2.2.1 Overflow condition                                  | 8  |

| 2.3 Motion Detection Mode                                   | 9  |

| 2.3.1 Description                                           | 9  |

| 2.3.2 Usage                                                 | 10 |

| 2.3.3 Examples                                              | 10 |

| 2.4 Free-Fall Detection                                     | 11 |

| 2.4.1 Description                                           |    |

| 2.4.2 Usage                                                 |    |

| 2.4.3 Example                                               |    |

|                                                             |    |

| 2.5 Ring Buffer                                             |    |

| 2.5.1 Description                                           |    |

| 2.5.2 Usage                                                 |    |

| 2.5.2.1 Overflow condition                                  |    |

| 2.5.3 Examples                                              | 12 |

| 2.6 Temperature measurement                                 | 13 |

| 2.6.1 Usage                                                 |    |

| 5                                                           |    |

| 2.7 Interrupt function (INT-pin)                            |    |

| 2.7.1 Usage                                                 | 13 |

| 2.8 Clock                                                   | 14 |

| B Addressing Space                                          | 15 |

|   | 3.1         | Register Description                         | .15 |

|---|-------------|----------------------------------------------|-----|

|   | 3.2         | Non-volatile memory                          | .16 |

|   | 3.3         | Output Registers                             | 16  |

|   | 3.4         | Configuration Registers                      | .19 |

|   | C           |                                              | 24  |

| 4 | Ser         | ial Interfaces                               | 24  |

|   | 4.1         | SPI Interface                                | 24  |

|   | 4.1.        |                                              |     |

|   | 4.1.        | 2 SPI bus error conditioning                 | .25 |

|   | 4.1.        |                                              |     |

|   |             | 1.3.1 Example of register read               |     |

|   |             | 1.3.2 Example of decremented register read   |     |

|   |             |                                              |     |

|   | 4.2<br>4.2. | I <sup>2</sup> C Interface                   |     |

|   |             | 2.1.1 I <sup>2</sup> C write mode            |     |

|   |             | 2.1.2 I <sup>2</sup> C read mode             |     |

|   |             | 2.1.3 Decremented register read              | .27 |

|   | 4.2.        | 2 Examples of I <sup>2</sup> C communication | .27 |

| 5 | Ele         | ctrical Characteristics                      | 28  |

| Ī |             |                                              |     |

|   | 5.1         | Absolute maximum ratings                     | .28 |

|   | 5.2         | Power Supply                                 | .28 |

|   | 5.3         | Digital I/O Specification                    | 28  |

|   | 5.3.        |                                              |     |

|   | 5.3.        |                                              |     |

|   | 5.3.        |                                              |     |

|   | 5.3.        | 4 I <sup>2</sup> C AC characteristics        | .30 |

| 6 | Pac         | kage Characteristics                         | 30  |

| Ĭ |             |                                              | 00  |

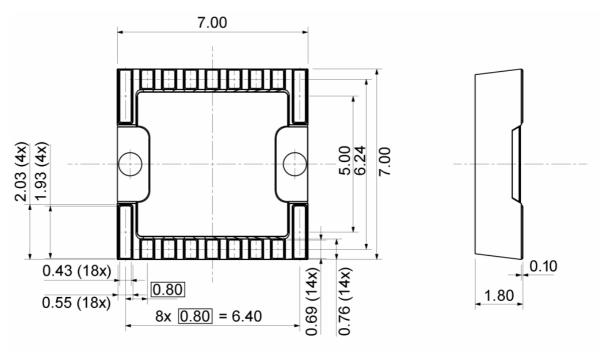

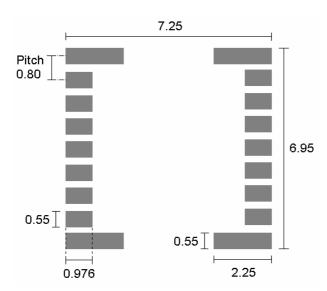

|   | 6.1         | Dimensions                                   | .30 |

| 7 | Δnr         | olication information                        | 21  |

| • | ΛPI         |                                              |     |

|   | 7.1         | Pin Description                              | .31 |

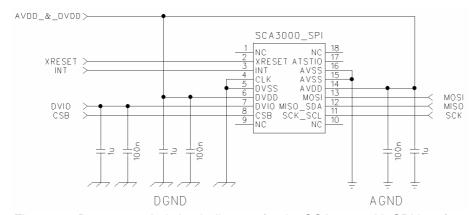

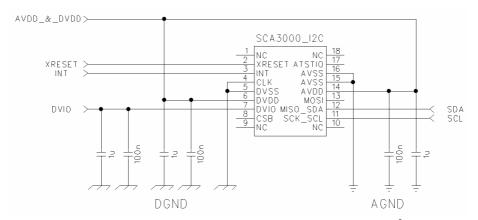

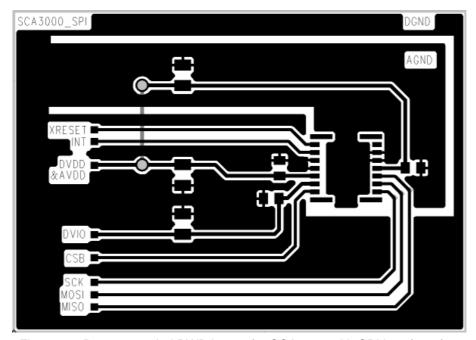

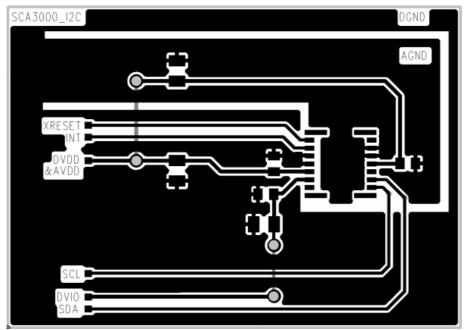

|   | 7.2         | Recommended circuit diagram                  | .31 |

|   | 7.3         | Recommended PWB layout                       | .32 |

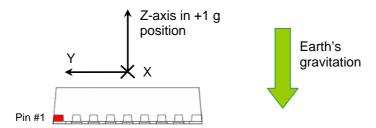

|   | 7.4         | Assembly instructions                        | 34  |

|   | 7.5         | Tape and reel specifications                 | .34 |

| 8 | Dat         | a sheet references                           | 25  |

| o | Dal         | a sileet i eieleilees                        | აა  |

|   | 8.1         | Offset                                       | .35 |

|   |             |                                              | -   |

| 8.1     | 1.1 Offset calibration error      | 35         |  |  |  |  |  |  |  |

|---------|-----------------------------------|------------|--|--|--|--|--|--|--|

| 8.1     | .1.2 Offset temperature error     |            |  |  |  |  |  |  |  |

|         | Sensitivity                       | 35         |  |  |  |  |  |  |  |

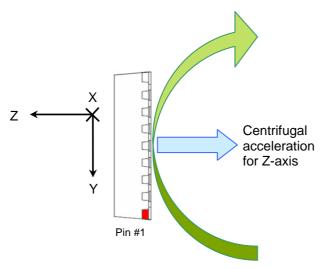

| · · · · | 2.1 Sensitivity calibration error | 3636       |  |  |  |  |  |  |  |

| 8.3     | Linearity                         |            |  |  |  |  |  |  |  |

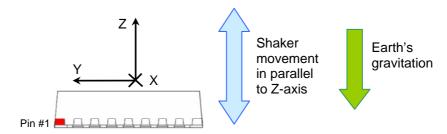

| 8.4     | Noise                             | 38         |  |  |  |  |  |  |  |

| 8.5     | Bandwidth                         | 38         |  |  |  |  |  |  |  |

| 8.6     | Cross-axis sensitivity            | 38         |  |  |  |  |  |  |  |

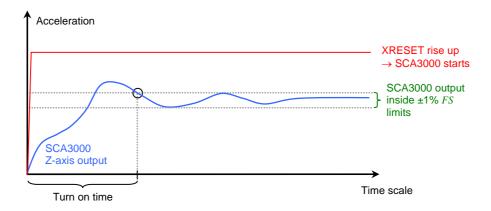

| 8.7     | Turn-on time                      | 39         |  |  |  |  |  |  |  |

| 9 Or    | der Information                   | 40         |  |  |  |  |  |  |  |

| 10 Do   | ocument Change Control            | 40         |  |  |  |  |  |  |  |

| 11 Co   | ontact Information                | <b>4</b> 1 |  |  |  |  |  |  |  |

## 1 General Description

#### 1.1 Introduction

SCA3000 is a three axis accelerometer family targeted for products requiring high performance with low power consumption. It consists of a 3D-MEMS sensing element and a signal conditioning ASIC packaged into a plastic Molded Interconnection Device package (MID).

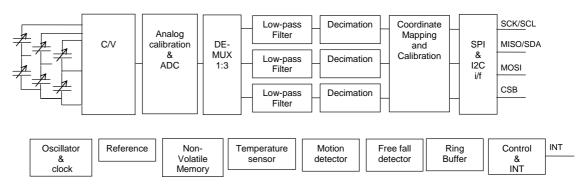

A block diagram of the SCA3000 product family is presented in Figure 1 below.

Figure 1. SCA3000 Block Diagram.

This document, no. 8257300, describes the product specification (e.g. operation modes, user accessible registers, electrical properties and application information) for the SCA3000 family. The specification for an individual sensor is available in the corresponding data sheet.

## 1.2 Functional Description

#### 1.2.1 Sensing element

The sensing element is manufactured using the proprietary bulk 3D-MEMS process, which enables robust, stable and low noise & power capacitive sensors.

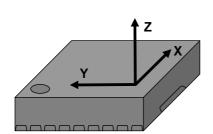

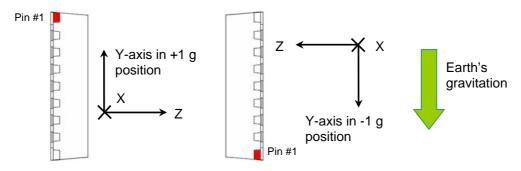

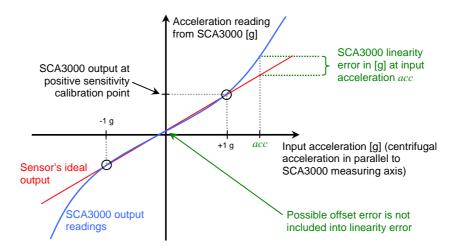

The sensing element consists of three acceleration sensitive masses. Acceleration will cause a capacitance change that will be then converted into a voltage change in the signal conditioning ASIC. Due to its mechanical construction, the element's measurement coordinates are rotated 45° compared to the conventional orthogonal X,Y,Z coordinate system.

## 1.2.2 Interface IC

The sensing element is interfaced via a capacitance-to-voltage (CV) converter. Following calibration in the analog domain, the signal is converted by a successive approximation type of analog-to-digital converter (ADC). The ADC's signal is de-multiplexed into three signal processing channels where it is low-pass filtered and decimated. After that, the signals are mapped into orthogonal coordinates (X-Y-Z) and transferred to the output registers. Depending on the product, the SCA3000 sensor supports either a fully digital serial SPI or I<sup>2</sup>C interface. In normal measurement mode, acceleration data can be read via the serial bus. Other supported features are a separate motion detection mode and parallel free-fall detection. In these modes, the sensor will generate an interrupt when a pre-defined condition has been met.

The SCA3000 includes an internal oscillator, reference and non-volatile memory that enable the sensor's autonomous operation within a system. The temperature sensor is used in some product applications to enhance the temperature stability. In that case, temperature information can also be read out from the device.

## 1.2.3 Factory calibration

Sensors are factory calibrated and the trimmed parameters are gain, offset and the frequency of the internal oscillator. Calibration parameters will be read automatically from the internal nonvolatile memory during sensor startup.

### 1.2.4 Supported features

Features supported by individual SCA3000 products are listed in Table 1 below.

Table 1. SCA3000 devices' summary.

| Features            | SCA3000-D01                           | SCA3000-D02                           | SCA3000-E01                           | SCA3000-E02                           | SCA3000-E04                           |

|---------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| Supply voltage      | 2.35 V – 3.6 V                        |

| I/O voltage         | 1.7 V – 3.6 V                         |

| Measuring range     | ±2 g                                  | ±2 g                                  | ±3 g                                  | ±3 g                                  | ±6 g                                  |

| Resolution          | 0.75mg / 0.04°                        | 0.75mg / 0.04°                        | 1mg / 0.06°                           | 1mg / 0.06°                           | 2mg / 0.11°                           |

| Sensitivity         | 1333 counts/g                         | 1333 counts/g                         | 1000 counts/g                         | 1000 counts/g                         | 500 counts/g                          |

| Output buffer       | User enabled,<br>64 samples /<br>axis |

| Motion detection    | User enabled                          |

| Free fall detection | User enabled                          |

| Interface           | SPI<br>max 1.8 MHz                    | I <sup>2</sup> C fast mode            | SPI<br>max 360 kHz                    | I <sup>2</sup> C std mode             | SPI<br>max 360 kHz                    |

| Temperature output  | Yes                                   | Yes                                   | No                                    | No                                    | No                                    |

| Clock               | Internal                              | Internal                              | Internal                              | Internal                              | Internal                              |

## 1.2.5 Operation modes

#### 1.2.5.1 Measurement

The SCA3000 is in normal measurement mode by default after start up. The sensor offers acceleration information via the SPI or I<sup>2</sup>C when the master requires it. The master can acquire one axis acceleration or all three axis acceleration depending on the application. Measurement resolution depends on the product type (see Table 1).

#### 1.2.5.2 Motion Detection

Motion Detection (MD) mode is intended to be used to save system level power consumption. In this mode, the SCA3000 activates the interrupt via the INT-pin when motion is detected. Sensitivity levels can be configured via the SPI or  $I^2C$  bus for each axis. Moreover, the detection condition can be defined using sensitivity directions with AND / OR / mux logic. Once the interrupt has happened, the detected direction can be read out from the corresponding status register.

Normal acceleration information is not available in MD mode.

#### 1.2.6 Free-Fall Detection

Free-Fall Detection (FFD) is intended to be used to save system resources. This feature activates the interrupt via the INT-pin when free-fall is detected. The minimum detectable distance depends on the individual product.

Normal acceleration information is available when the FFD is enabled.

#### 1.2.7 Interrupt

The SCA3000 has a dedicated output pin (INT) to be used as the interrupt for the master controller. Interrupt conditions can be activated and deactivated via the SPI or I<sup>2</sup>C bus. Once the interrupt has happened, the interrupt source can be read out from the corresponding status register.

## 1.2.8 Temperature output

Some SCA3000 products provide 9-bit temperature information via the serial interface. See Table 1 for detailed product information.

## 1.2.9 Output ring buffer

In those applications where real time acceleration information is not needed, the ring buffer memory can be used to buffer acceleration data. This will release  $\mu C$  resources for other tasks or for example, to offer a power saving mode while SCA3000 samples acceleration data into its buffer memory.

Acceleration data is sampled at a constant sample rate by the sensor. The buffer is a FIFO type (First In First Out) where the oldest data is shifted out first. It has separate read and write address pointers, so it can be read and written simultaneously. If the buffer overflows, the oldest data is lost and the new data replaces the oldest samples.

Ring buffer logic can be configured to give an interrupt when the buffer is ½ or ¾ full. The entire ring buffer content can be read by one read sequence.

## 2 Reset and power up, Operation Modes, HW functions and Clock

## 2.1 Reset and power up

The SCA3000 has an external active low reset pin. Power supplies must be within the specified range before the reset can be released.

After releasing the reset, the SCA3000 will read configuration and calibration data from the non-volatile memory to volatile registers. Then the SCA3000 will make a check sum calculation to the read memory content. The STATUS register's CSME-bit="0" shows successful memory read operation.

### 2.2 Measurement Mode

## 2.2.1 Description

The SCA3000 enters the measurement mode by default after power-on and the CV-converter will start to feed data to the signal channel (Figure 1). Data will be reliable in the output registers after the product specific turn-on time.

The SCA3000 can also be set to optional measurement modes. See component specific data sheets for detailed functional parameters in all measurement modes. All available measurement modes for the SCA3000 are described in Table 2 below.

Table 2. Available measurement modes for SCA3000.

| Available measurement modes     | SCA3000-D0x             | SCA3000-E0x                  |

|---------------------------------|-------------------------|------------------------------|

| Default after power-on or reset | Measurement mode        | Measurement mode             |

| Optional measurement mode       | Bypass measurement mode | Narrow band measurement mode |

### 2.2.1.1 Bypass measurement mode

In bypass measurement mode, the signal bandwidth of the SCA3000 is extended by bypassing the low-pass filter in signal channel. As a result of a wider measurement bandwidth, the noise level is higher.

#### 2.2.1.2 Narrow band measurement mode

In narrow band measurement mode, the signal bandwidth of the SCA3000 is reduced by increasing low-pass filtering in signal channel. In addition, the output data rate is halved due to decimation. As a result of a narrower signal bandwidth, the noise level is lower.

#### 2.2.2 **Usage**

The optional measurement mode can be enabled by MODE bits in MODE register to "010". See section 3.4 for MODE register details.

Acceleration data can be read from data output registers X\_LSB, X\_MSB, Y\_LSB, Y\_MSB, Z\_LSB and Z\_MSB in all measurement modes. Each of these registers can be read one by one or using the decrement register read, which is described in section 4.1.3.2 for SPI and 4.2.1.3 for I<sup>2</sup>C interface. See section 3.3 for output register details.

#### 2.2.2.1 Overflow condition

Since acceleration data registers have no limiter, the possible overflow needs to be detected using bits [B7, B6, B5]. If bits [B7, B6, B5] are '011' or '100', data overflow has occurred (see Table 3). This applies for all acceleration output registers (X\_LSB ... Z\_MSB and BUF\_DATA).

Table 3. Overflow bit patterns in acceleration data registers (X LSB ... Z MSB and BUF DATA).

| Byte                                   | MSB  | SB byte |     |    |    |    |    | LSB byte |    |    |    |    |    |       |

|----------------------------------------|------|---------|-----|----|----|----|----|----------|----|----|----|----|----|-------|

| Bit number                             | B7   | B6      | B5  | B4 | В3 | B2 | B1 | B0       | B7 | B6 | B5 | B4 | В3 | B2:B0 |

| Acceleration [mg]                      | Sign | d11     | d10 | d9 | d8 | d7 | d6 | d5       | d4 | d3 | d2 | d1 | d0 |       |

| Data overflow on positive acceleration | 0    | 1       | 1   | Х  | X  | х  | Х  | х        | x  | х  | x  | x  | Х  | xxx   |

| Data overflow on negative acceleration | 1    | 0       | 0   | Х  | x  | x  | Х  | х        | x  | х  | x  | x  | Х  | xxx   |

| x = ignore                             |      |         |     |    |    |    |    |          |    |    |    |    |    |       |

In case of overflow, the output register value must be discarded. When an overflow is detected, the bit pattern '0 1011 1111 1111' is used for positive accelerations and '1 0100 0000 0000' for negative accelerations until a valid acceleration value is read. In Table 4 the maximum and minimum acceleration register values that are in measuring range (for registers X\_LSB ... Z\_MSB) for SCA3000-D0x and SCA3000-E0x are presented.

Table 4. Maximum and minimum values in the SCA3000 measuring range.

|                                        |             | SCA3000-D01<br>SCA3000-D02 | SCA3000-E01<br>SCA3000-E02 | SCA3000-E04       |

|----------------------------------------|-------------|----------------------------|----------------------------|-------------------|

| First positive                         | [mg]        | -                          | -                          | -                 |

| acceleration value                     | dec         | 3072                       | 3072                       | 3072              |

| out of range                           | bin         | 0 1100 0000 0000           | 0 1100 0000 0000           | 0 1100 0000 0000  |

| Maximum positive                       | [mg]        | 2303.25 mg                 | 3071 mg                    | 6142 mg           |

| acceleration value in                  | dec         | 3071                       | 3071                       | 3071              |

| range                                  | bin         | 0 1011 1111 1111           | 0 1011 1111 1111           | 0 1011 1111 1111  |

| Minimum negative acceleration value in | [mg]<br>dec | -2304 mg<br>-3072          | -3072 mg<br>-3072          | -6144 mg<br>-3072 |

| range                                  | bin         | 1 0100 0000 0000           | 1 0100 0000 0000           | 1 0100 0000 0000  |

| First negative                         | [mg]        | -                          | -                          | -                 |

| acceleration value                     | dec         | -3073                      | -3073                      | -3073             |

| out of range                           | bin         | 1 0011 1111 1111           | 1 0011 1111 1111           | 1 0011 1111 1111  |

#### 2.3 Motion Detection Mode

## 2.3.1 Description

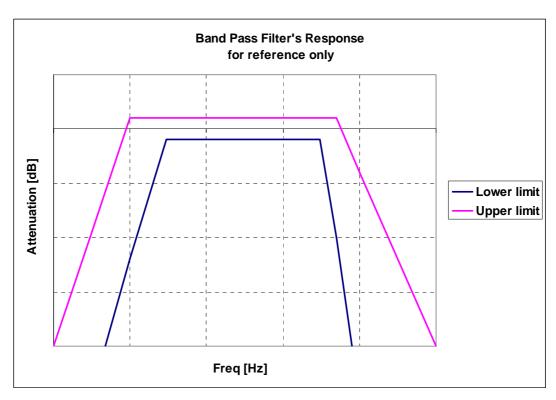

In MD mode, the ADC's data is not fed to the signal processing channel shown in Figure 1 but to the MD block. It consists of a digital band-pass filter (BPF), threshold level programmable digital comparator and a configurable trigger function.

BPF's -3 dB high-pass frequency is 25 Hz ...60 Hz and -3 dB low-pass frequency is 0.05 Hz ...1 Hz. See Figure 2 below.

Figure 2. The MD band-pass filter's frequency response.

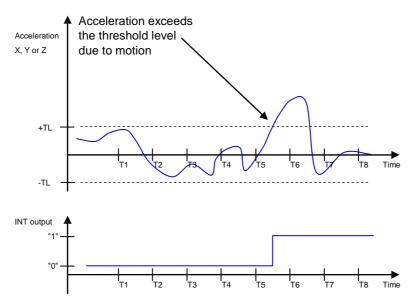

The absolute value of programmable Threshold Level (TL) is 0 < |TL| < FS g (FS is sensor full scale measuring range). NOTE: Due to power consumption optimization, the step size between each step and axis is not the same, see section 3.4 for threshold level details.

The triggering condition can be defined using OR/AND logic:

- 1. Any sensing direction can be configured to trigger the interrupt (OR condition).

- 2. Any sensing direction can be configured to be required to trigger the interrupt (AND condition).

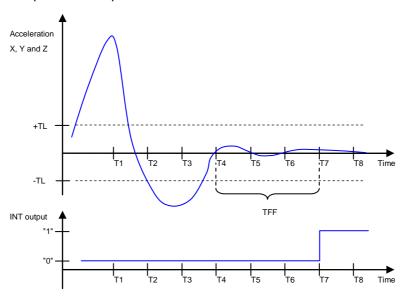

Figure 3. Motion detector operation.

#### 2.3.2 Usage

The MD mode can be enabled by setting the MODE bits in the MODE register to "011". The trigger condition can be defined by setting REQ\_Z, REQ\_Y, REQ\_X, EN\_Z, EN\_Y and EN\_X bits in MD\_CTRL register and Z\_TH, Y\_TH and Z\_TH bits in MD\_Z\_TH, MD\_Y\_TH and MD\_X\_TH registers, respectively. See section 3.4 for the configuration register and section 2.7 for the interrupt functionality details.

In MD mode, acceleration data is not available in registers X\_LSB, X\_MSB, Y\_LSB, Y\_MSB, Z\_LSB, Z\_MSB and BUF\_DATA.

#### 2.3.3 Examples

A simple example of motion detection usage:

- 1. Write "00000011" (03h) into the MODE register (enable motion detection mode, MODE = '011').

- 2. Acceleration data is not available when the SCA3000 is in motion detection mode.

- The INT-pin is activated when motion is detected, see section 2.7 for detailed INT-pin information.

In the next example, the motion detector is configured to give an interrupt on motion only in the X-OR Y-axis direction:

- 1. Write "00000011" (03h) into MODE register (enable motion detection mode, MODE = '011')

- 2. Write "00000000" (00h) into UNLOCK register

- 3. Write "01010000" (50h) into UNLOCK register \rightarrow Unlock sequence for register lock

- 4. Write "10100000" (A0h) into UNLOCK register

- 5. Write "00000010" (02h) into CTRL\_SEL register (to select indirect MD\_CTRL register)

- 6. Write "00000011" (03h) into CTRL\_DATA register (this data is written into MD\_CTRL register, enable trigger on Y-channel, EN\_Y = '1', enable trigger on X-channel, EN\_X = '1')

- 7. Acceleration data is not available when the SCA3000 is in motion detection mode

- 8. The INT-pin is activated when motion is detected in the X- or Y-axis direction (Z-axis direction is ignored), see section 2.7 for detailed INT-pin information.

#### 2.4 Free-Fall Detection

## 2.4.1 Description

During free-fall in the gravitation field, all 3 orthogonal acceleration components are ideally equal to zero. Due to practical non-idealities, detection must be done using Threshold Level (TL) greater than 0.

When enabled, the Free-Fall Detection (FFD) will monitor 8 MSB's of the measured acceleration in the X, Y and Z directions. If the measured acceleration stays within the TL longer than time TFF (Figure 4 below), which corresponds approx 25 cm drop distance, the FFD will generate an interrupt to the INT-pin.

Figure 4. Free Fall condition.

#### 2.4.2 Usage

Free-fall detection can be enabled by setting FFD\_EN bit in MODE register to "1". See section 3.4 for MODE register details.

Acceleration data is available in registers X\_LSB, X\_MSB, Y\_LSB, Y\_MSB, Z\_LSB, Z\_MSB and BUF\_DATA as in measurement mode. See section 3.3 for output register and section 2.7 for interrupt functionality details.

#### 2.4.3 Example

A simple example of free-fall detection usage:

- 1. Write "00010000" (10h) into the MODE register (enable free fall detection, FDD\_EN = '1')

- 2. Acceleration data can be read normally

- 3. INT-pin is activated when free fall is detected, see section 2.7 for detailed INT-pin information.

## 2.5 Ring Buffer

## 2.5.1 Description

The SCA3000's Ring Buffer is a 192 acceleration data samples long (64 samples of 11 bit three axis data) internal memory to relax the real-time operation requirements of the host processor. The following parameters are configurable:

- 1. Each measurement axis can be individually disabled. If measurement data from e.g. Y-axis is not needed, available memory can be used for X- and Z-axis data.

- 2. Buffer data length can be changed from 11 to 8 bits. In 8-bit mode, data can be read out using shorter read sequence.

- 3. Ring buffer's input sample rate can be the same as the sensor's data rate or divided by 2 or 4. When the divider is e.g. 2, only every 2<sup>nd</sup> acceleration data will be stored.

- 4. The Interrupt condition, when enabled, can be selected between two: interrupt in INT-pin occurs when the buffer is 50% or 75% full.

## 2.5.2 Usage

The ring buffer can be enabled by setting BUF\_EN bit in MODE register to "1". After enabling the buffer, acceleration data can be read from BUF\_DATA register using decrement register read, which is described in section 4.1.3.2 for SPI and 4.2.1.3 for I<sup>2</sup>C interface.

Each measurement axis can be individually disabled by setting corresponding bits in BUF\_X\_EN, BUF\_Y\_EN and BUF\_Z\_EN in OUT\_CTRL register to "0".

Output data length can be changed from 11 bits to 8 bits by setting bit BUF\_8BIT in MODE register to "1". See section 3.3 for bit level descriptions.

The count of available data samples in output ring buffer can be read from BUF\_COUNT register. Register value is updated only when it is accessed over the SPI or I<sup>2</sup>C.

Data shift out order is X,Y,Z. In 11 bit mode two bytes must be read to get all 11 bits out. In that case, the MSB byte is 1<sup>st</sup>. Examples:

- 1. 11 bits data length, X&Y&Z axis enabled: X1\_MSB, X1\_LSB, Y1\_MSB, Y1\_LSB, Z1\_MSB, Z1\_LSB, X2\_MSB, X2\_LSB, ... latest Z LSB

- 11 bits data length, Y&Z axis enabled: Y1\_MSB, Y1\_LSB, Z1\_MSB, Z1\_LSB, Y2\_MSB, Y2\_LSB, Z2\_MSB, Z2\_LSB, Y3\_MSB, Y3\_LSB, ..., latest Z\_LSB

- 3. 8 bits data length, all axis enabled: X1, Y1, Z1, X2, Y2, Z2,..., latest Z

- 4. 8 bits data length, X&Z axis enabled: X1, Z1, X2, Z2, X3, Z3, ..., latest Z

- 5. 8 bits data length, Z axis enabled: Z1, Z2, Z3, ..., latest Z

See section 2.7 for interrupt functionality details.

Acceleration data is available in X\_LSB, X\_MSB, Y\_LSB, Y\_MSB, Z\_LSB and Z\_MSB when the ring buffer is enabled.

## 2.5.2.1 Overflow condition

Overflow is detected from data ring buffer in same way as from the output registers. See section 2.2.2.1 for details.

#### 2.5.3 Examples

A simple example of output ring buffer usage:

- 1. Write "10000000" (C0h) into MODE register (enable output ring buffer, BUF\_EN = '1')

- 2. Acceleration data can be read normally

- 3. INT-pin is activated when buffer is ½ full, see section 2.7 for detailed INT-pin information.

In the next example, the output Ring Buffer is configured to sample only the Z-axis acceleration data with 8 bit resolution and reduced data rate (only every second sample is stored into output ring buffer). In addition, the SCA3000 is configured to give an interrupt when the output ring buffer is ¾ full:

- 1. Write "11000000" (C0h) into the MODE register (enable output ring buffer, BUF EN = '1', set data length to 8 bits, BUF 8BIT = '1')

- Write "00000000" (00h) into UNLOCK register

- Write "01010000" (50h) into UNLOCK register

Write "10100000" (A0h) into UNLOCK register

- 5. Write "00001011" (0Bh) into CTRL\_SEL register (to select indirect OUT\_CTRL register)

- 6. Write "00000101" (03h) into CTRL\_DATA register (this data is written into OUT\_CTRL register, store Z-axis data, BUF\_Z\_EN = '1', divide data rate by 2, BUF\_RATE = '01')

- Write "10000001" (81h) into INT\_MASK register (set buffer interrupt level to 3/4 full, BUF\_F\_EN = '1', set INT-pin to active high, INT\_ACT = '1')

- 8. Acceleration data can be read normally for all axis and with full resolution. The buffer data can be read from BUF\_DATA register

- 9. INT-pin is activated when the output ring buffer is \(^3\) full of Z-axis acceleration data, see section 2.7 for detailed INT-pin information.

## Temperature measurement

## 2.6.1 Usage

Nine bit temperature information is available in the TEMP\_MSB and TEMP\_LSB registers, if the feature is enabled in the product (see Table 1). The TEMP\_MSB register must be read before the TEMP LSB register in order to get valid temperature data. Registers are updated with the latest temperature data when accessed. See section 3.3 for register details.

The temperature registers' typical output at +23 °C is 256 counts and a 1 °C change in temperature typically corresponds to a 1.8 LSB change in the SCA3000 temperature output. Temperature information is converted to [°C] as follows

#### **Equation 1**

$$Temp[°C] = 23°C + \frac{Temp_{dec} - 256LSB}{1.8 \frac{LSB}{°C}}$$

where  $Temp[^{\circ}C]$  is temperature in Celsius and  $Temp_{dec}$  is the temperature from TEMP\_MSB and TEMP\_LSB registers in decimal format.

## 2.7 Interrupt function (INT-pin)

## 2.7.1 Usage

The Motion Detector and Free Fall Detector will generate an interrupt to INT-pin when the corresponding function is enabled and the interrupt condition is met. The SCA3000's ring buffer will generate an interrupt when interrupt functionality has been enabled. Setting BUF\_F\_EN bit in INT\_MASK register "1" results in interrupt when the register is 75% full. Setting BUF\_H\_EN bit in INT MASK register "1" results in interrupt when the register is 50% full.

Setting INT\_ALL bit in INT\_MASK register will mask all interrupts.

The interrupt polarity (active high/low) can be configured with INT\_MASK register's INT\_ACT bit.

Once the interrupt has happened, the INT\_STATUS register must be read to acknowledge the interrupt.

- 1. If at least one of MD bits in INT\_STATUS register is "1", motion has been detected.

- 2. If FFD bit in INT\_STATUS register is "1", free-fall has been detected.

- 3. If BUF\_FULL bit is "1", Ring Buffer is 75% full. Correspondingly, if BUF\_HALF is "1", the Ring Buffer is 50% full.

See section 3.3 for INT\_STATUS register details.

## 2.8 Clock

The SCA3000 has an internal factory trimmed oscillator and clock generator. Internal frequencies vary product by product.

## 3 Addressing Space

The SCA3000 register contents and bit definitions are described in more detail in the following sections.

## 3.1 Register Description

The SCA3000 addressing space is presented in Table 5 below.

Table 5. List of registers.

| Add.             | Name       | Description                                                                                                                                                  | Mode<br>(R, W, RW, IA) | Reg.<br>type | Locked |

|------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------|--------|

| 00h              | REVID      | ASIC revision ID number                                                                                                                                      | R                      | Conf         |        |

| 01h              |            | Reserved                                                                                                                                                     |                        |              | -      |

| 02h              | STATUS     | Status register                                                                                                                                              | R                      | Conf         |        |

| 03h              |            | Reserved                                                                                                                                                     |                        |              | -      |

| 04h              | X_LSB      | X-axis LSB frame                                                                                                                                             | R                      | Output       |        |

| 05h              | X_MSB      | X-axis MSB frame                                                                                                                                             | R                      | Output       |        |

| 06h              | Y_LSB      | Y-axis LSB frame                                                                                                                                             | R                      | Output       |        |

| 07h              | Y_MSB      | Y-axis MSB frame                                                                                                                                             | R                      | Output       |        |

| 08h              | Z_LSB      | Z-axis LSB frame                                                                                                                                             | R                      | Output       |        |

| 09h              | Z_MSB      | Z-axis MSB frame                                                                                                                                             | R                      | Output       |        |

| 0Ah 0Eh          |            | Reserved                                                                                                                                                     |                        |              | -      |

| 0Fh              | BUF_DATA   | Ring buffer output register                                                                                                                                  | R                      | Output       |        |

| 10h 11h          |            | Reserved                                                                                                                                                     |                        |              | -      |

| 12h              | TEMP_LSB   | Temperature LSB frame                                                                                                                                        | R                      | Output       |        |

| 13h              | TEMP_MSB   | Temperature MSB frame                                                                                                                                        | R                      | Output       |        |

| 14h              | MODE       | Operating mode selection, control and configuration for: - mode selection - output buffer - free-fall detection                                              | RW                     | Conf         |        |

| 15h              | BUF_COUNT  | Count of unread data samples in output buffer                                                                                                                | R                      | Output       |        |

| 16h              | INT_STATUS | Interrupt status register:  - output buffer is not full, ½ full or ¾ full  - free-fall detected / not detected  - information of which axis triggered motion | R                      | Output       |        |

| 17h              | I2C_RD_SEL | Register address for I <sup>2</sup> C read operation                                                                                                         | RW                     | Conf         |        |

| 18h              | CTRL_SEL   | Register address pointer for indirect control registers                                                                                                      | RW                     | Conf         | Х      |

| 19h<br>          |            | Reserved                                                                                                                                                     |                        |              | _      |

| 1Dh              |            |                                                                                                                                                              |                        |              |        |

| 1Eh              | UNLOCK     | Unlock register                                                                                                                                              | RW                     | Conf         |        |

| 1Fh 20h          |            | Reserved                                                                                                                                                     |                        |              | -      |

| (coi<br>INT<br>- |            | HW interrupt mask register (configures the operation of INT-pin): - interrupt when output buffer is ¾ full (enable / disable)                                | RW, NV                 | Conf         |        |

| Add.    | Name      | Description                                                                                                                                                                          | Mode<br>(R, W, RW, IA) | Reg.<br>type | Locked |

|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------|--------|

|         |           | <ul> <li>interrupt when output buffer is ½ full (enable / disable)</li> <li>mask all interrupts on INT-pin (enable / disable)</li> <li>INT-pin activity (INT active high)</li> </ul> |                        |              |        |

| 22h     | CTRL_DATA | Data to/from register which address is in CTRL_SEL (18h) register                                                                                                                    | RW, NV, IA             | Conf         | Χ      |

| 23h 3Fh |           | Reserved                                                                                                                                                                             |                        |              | -      |

Add. is the register address in hex format.

RW – Read / Write register, R – Read-only register, NV – Register mirrors NV-memory data (NV = non-volatile).

IA - indirect addressing used.

Registers whose read and write access is blocked by register lock is marked in "Locked" column.

## 3.2 Non-volatile memory

The SCA3000 has an internal non-volatile memory for calibration and configuration data. Memory content will be programmed during production and is not user configurable. Initial configuration values can be found in the following section 3.4.

## 3.3 Output Registers

The SCA3000 output register (marked with 'Output' in Table 5) contents and bit definitions are described in this section. Output registers contain information of measured acceleration and temperature as well as information of the operating state and interrupts of SCA3000.

Address: 04h

Register name: X\_LSB, X-axis LSB frame

| Bits | Mode | Initial<br>Value | Name | Description      |

|------|------|------------------|------|------------------|

| 7:0  | R    | 00h              | DATA | X-axis LSB frame |

Address: 05h

Register name: X MSB, X-axis MSB frame

| Bits | Mode | Initial<br>Value | Name | Description      |

|------|------|------------------|------|------------------|

| 7:0  | R    | 00h              | DATA | X-axis MSB frame |

Address: 06h

Register name: Y\_LSB, Y-axis LSB frame

| Bits | Mode | Initial<br>Value | Name | Description      |

|------|------|------------------|------|------------------|

| 7:0  | R    | 00h              | DATA | Y-axis LSB frame |

Address: 07h

Register name: Y\_MSB, Y-axis MSB frame

| Bits | Mode | Initial<br>Value | Name | Description      |

|------|------|------------------|------|------------------|

| 7:0  | R    | 00h              | DATA | Y-axis MSB frame |

Address: 08h

Register name: Z\_LSB, Z-axis LSB frame

| Bits | Mode | Initial<br>Value | Name | Description      |

|------|------|------------------|------|------------------|

| 7:0  | R    | 00h              | DATA | Z-axis LSB frame |

Address: 09h

Register name: Z\_MSB, Z-axis MSB frame

| Bits | Mode | Initial<br>Value | Name | Description      |

|------|------|------------------|------|------------------|

| 7:0  | R    | 00h              | DATA | Z-axis MSB frame |

Address: 0Fh

Register name: BUF\_DATA, ring buffer output register

| Bits | Mode | Initial<br>Value | Name | Description                 |

|------|------|------------------|------|-----------------------------|

| 7:0  | R    | 00h              | DATA | Ring buffer output register |

The bit level description for acceleration data from X\_LSB ... Z\_MSB and BUF\_DATA registers is presented in Table 6, Table 7 and Table 8. The acceleration data is presented in 2's complement format. At 0 g acceleration the output is ideally 00h.

Table 6. Bit level description for acceleration registers of SCA3000-D01 and SCA3000-D02.

| Byte                                  | MSB  | byte |     |     |     |    |    |    | LSB | byte |    |     |      |       |

|---------------------------------------|------|------|-----|-----|-----|----|----|----|-----|------|----|-----|------|-------|

| Bit number                            | B7   | B6   | B5  | B4  | В3  | B2 | B1 | B0 | B7  | B6   | B5 | B4  | В3   | B2:B0 |

| Acceleration [mg]                     | Sign | 1536 | 768 | 384 | 192 | 96 | 48 | 24 | 12  | 6    | 3  | 1.5 | 0.75 | XXX   |

| SCA3000-D01,-D02<br>[X_LSBZ_MSB]      | s    | d11  | d10 | d9  | d8  | d7 | d6 | d5 | d4  | d3   | d2 | d1  | d0   | xxx   |

| SCA3000-D01,-D02                      |      |      |     |     |     |    |    |    |     |      |    |     |      |       |

| Ring buffer in 11-bit mode [BUF_DATA] | S    | d9   | d8  | d7  | d6  | d5 | d4 | d3 | d2  | d1   | d0 | X   | Χ    | XXX   |

| SCA3000-D01,-D02                      |      |      |     |     |     |    |    |    |     |      |    |     |      |       |

| Ring buffer in 8-bit mode [BUF_DATA]  | S    | d6   | d5  | d4  | d3  | d2 | d1 | d0 | Х   | Х    | Х  | Х   | Χ    | XXX   |

s = sign bit

Table 7. Bit level description for acceleration registers of SCA3000-E01 and SCA3000-E02.

| Byte                                                        | MSB  | byte |      |     |     |     |    |    | LSB | byte |    |    |    |       |

|-------------------------------------------------------------|------|------|------|-----|-----|-----|----|----|-----|------|----|----|----|-------|

| Bit number                                                  | B7   | B6   | B5   | B4  | В3  | B2  | B1 | B0 | B7  | B6   | B5 | B4 | В3 | B2:B0 |

| Acceleration [mg]                                           | Sign | 2048 | 1024 | 512 | 256 | 128 | 64 | 32 | 16  | 8    | 4  | 2  | 1  | XXX   |

| SCA3000-E01,-D02<br>[X_LSBZ_MSB]                            | s    | d11  | d10  | d9  | d8  | d7  | d6 | d5 | d4  | d3   | d2 | d1 | d0 | xxx   |

| SCA3000-E0,-D02<br>Ring buffer in 11-bit<br>mode [BUF_DATA] | s    | d9   | d8   | d7  | d6  | d5  | d4 | d3 | d2  | d1   | d0 | X  | Х  | XXX   |

| SCA3000-E0,-D02<br>Ring buffer in 8-bit<br>mode [BUF_DATA]  | s    | d6   | d5   | d4  | d3  | d2  | d1 | d0 | х   | x    | х  | х  | х  | xxx   |

s = sign bit

x = not used bit

Table 8. Bit level description for acceleration registers of SCA3000-E04.

| Byte                                                   | MSB  | byte |      |      |     |     |     |    | LSB | byte |    |    |    |       |

|--------------------------------------------------------|------|------|------|------|-----|-----|-----|----|-----|------|----|----|----|-------|

| Bit number                                             | B7   | B6   | B5   | B4   | В3  | B2  | B1  | B0 | B7  | B6   | B5 | B4 | В3 | B2:B0 |

| Acceleration [mg]                                      | Sign | 4096 | 2048 | 1024 | 512 | 256 | 128 | 64 | 32  | 16   | 8  | 4  | 2  | XXX   |

| SCA3000-E04<br>[X_LSBZ_MSB]                            | s    | d11  | d10  | d9   | d8  | d7  | d6  | d5 | d4  | d3   | d2 | d1 | d0 | xxx   |

| SCA3000-E4<br>Ring buffer in 11-bit<br>mode [BUF_DATA] | S    | d9   | d8   | d7   | d6  | d5  | d4  | d3 | d2  | d1   | d0 | х  | X  | XXX   |

| SCA3000-E4<br>Ring buffer in 8-bit<br>mode [BUF_DATA]  | s    | d6   | d5   | d4   | d3  | d2  | d1  | d0 | х   | X    | х  | Х  | х  | XXX   |

s = sign bit

Address: 12h

Register name: TEMP\_LSB, temperature LSB frame

| Bits | Mode | Initial<br>Value | Name | Description           |

|------|------|------------------|------|-----------------------|

| 7:0  | R    | 00h              | TEMP | Temperature LSB frame |

Address: 13h

Register name: TEMP\_MSB, temperature MSB frame

| Bits | Mode | Initial<br>Value | Name | Description           |

|------|------|------------------|------|-----------------------|

| 7:0  | R    | 00h              | TEMP | Temperature MSB frame |

The bit level description for temperature data from TEMP\_MSB and TEMP\_LSB registers is presented in Table 9. Temperature data is presented in unsigned format. See section 2.6 for more detailed information of converting the data to temperature in [°C].

Table 9. Bit level description for temperature registers [TEMP\_MSB ... TEMP\_LSB].

| Register                    | TEMP_ | _MSB |       |       |       |      |      | TEMP. | LSB  |       |       |

|-----------------------------|-------|------|-------|-------|-------|------|------|-------|------|-------|-------|

| Bit number                  | B7:B6 | B5   | B4    | В3    | B2    | B1   | B0   | B7    | B6   | B5    | B4:B0 |

| Temperature [°C]            | XX    | ~142 | ~71.1 | ~35.5 | ~17.8 | ~8.9 | ~4.4 | ~2.2  | ~1.1 | ~0.56 | XXXXX |

| Bit in temperature register | XX    | t8   | t7    | t6    | t5    | t4   | t3   | t2    | t1   | tO    | xxxxx |

x = not used bit

Address: 15h

Register name: BUF\_COUNT, output ring buffer status

| Bits | Mode | Initial<br>Value | Name  | Description                                            |

|------|------|------------------|-------|--------------------------------------------------------|

| 7:0  | R    | 00h              | COUNT | Count of available data samples in output ring buffer. |

x = not used bit

Address: 16h

Register name: INT\_STATUS, interrupt status register (all interrupts that are available in current

operation mode)

| Bits | Mode | Initial<br>Value | Name     | Description                                                                                                             |

|------|------|------------------|----------|-------------------------------------------------------------------------------------------------------------------------|

| 7    | R    | 0                | BUF_FULL | Output ring buffer is ¾ full<br>1 – Ring buffer is ¾ full<br>0 – Ring buffer is not full                                |

| 6    | R    | 0                | BUF_HALF | Output ring buffer is ½ full 1 – Ring buffer is ½ full 0 – Ring buffer is not full                                      |

| 5:4  |      |                  |          | Reserved                                                                                                                |

| 3    | R    | 0                | FFD      | Free-fall detection 1 – Free-fall detected (0 g acceleration) 0 – Free-fall not detected                                |

| 2:0  | R    | 000              | MD       | Motion detector triggered channel indication  1xx – Trigger on Y-axis  x1x – Trigger on X-axis  xx1 – Trigger on Z-axis |

## 3.4 Configuration Registers

SCA3000 configuration register (marked with 'Conf' in Table 5) contents and bit definitions are described in this section. Configuration registers are used to configure SCA3000 operation and the operation parameters.

Address: 00h

Register name: REVID, ASIC revision ID number tied in metal

| Bits | Mode | Initial<br>Value | Name   | Description           |

|------|------|------------------|--------|-----------------------|

| 7:4  | R    |                  | REVMAJ | Major revision number |

| 3:0  | R    |                  | REVMIN | Minor revision number |

Address: 02h

Register name: STATUS, status register

| Bits | Mode | Initial<br>Value | Name      | Description                                                                                                |

|------|------|------------------|-----------|------------------------------------------------------------------------------------------------------------|

| 7:6  |      |                  |           | Reserved                                                                                                   |

| 5    | R    | 0                | LOCK      | Status of lock register 0 – Lock is closed 1 – Lock is open                                                |

| 4:2  |      |                  |           | Reserved                                                                                                   |

| 1    | R    | 0                | CSME      | EEPROM checksum error 1 – EEPROM checksum error 0 – No error                                               |

| 0    | R    | 0                | SPI_FRAME | SPI frame error. Bit is reset, when next correct SPI frame is received.  1 – SPI frame error  0 – No error |

Address: 14h

Register name: MODE, operation mode selection

| Bits | Mode | Initial<br>Value | Name     | Description                                                                                                                                                                                                      |

|------|------|------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | RW   | 0                | BUF_EN   | Output ring buffer<br>1 – Enabled<br>0 – Disabled (Buffer in power down)                                                                                                                                         |

| 6    | RW   | 0                | BUF_8BIT | Output ring buffer data length  1 – Ring buffer is read in single 8 bit frame per stored axis (8 bit mode)  0 – Ring buffer is read in two 8 bit frames per stored axis (11 bit mode). Unused bits are set to 0. |

| 5    |      |                  |          | Reserved                                                                                                                                                                                                         |

| 4    | RW   | 0                | FFD_EN   | Free-fall detection 1 – Enabled 0 – Disabled (detection in power down)                                                                                                                                           |

| 3    |      |                  |          | Reserved                                                                                                                                                                                                         |

| 2:0  | RW   | 000              | MODE     | Selects SCA3000 series operation mode  000 – Normal measurement mode  010 – Optional measurement mode  (see Table 2)  011 – MD, Motion Detector  Other combinations are reserved                                 |

Address: 17h

Register name: I2C\_RD\_SEL, register address for I<sup>2</sup>C read operation

| Bits | Mode | Initial<br>Value | Name | Description                                                                                                  |

|------|------|------------------|------|--------------------------------------------------------------------------------------------------------------|

| 7:0  | W    | 00h              | ADDR | Address of register to be read via I <sup>2</sup> C. Register is used only for I <sup>2</sup> C read access. |

Address: 18h

Register name: CTRL\_SEL, Control register selector, UNLOCK REQUIRED

| Bits | Mode | Initial<br>Value | Name   | Description                                                                                                                                                                                                                                                                                                                          |

|------|------|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5  | RW   | 000              |        | Reserved                                                                                                                                                                                                                                                                                                                             |

| 4:0  | RW   | 00000            | SELECT | Indirect control registers, select register address for read / write access 00010 – MD_CTRL (Motion Detector control) 00011 – MD_Y_TH (Motion Detector Y- threshold) 00100 – MD_X_TH (Motion Detector X- threshold) 00101 – MD_Z_TH (Motion Detector Z- threshold) 01011 – OUT_CTRL (Output control) Other combinations are reserved |

CTRL\_SEL register works as an address pointer for registers listed below. When this register is written the content of selected register is available for reading/writing from/to register CTRL\_DATA.

Address value: 00010

Register name: MD\_CTRL, Motion Detector control (Indirect access via CTRL\_SEL)

| Bits | Initial<br>Value | Name  | Description                                                                 | Note                                                               |

|------|------------------|-------|-----------------------------------------------------------------------------|--------------------------------------------------------------------|

| 7:6  |                  |       | Reserved                                                                    |                                                                    |

| 5    | 0                | REQ_Z | <ul><li>1 – Require trigger on Z-channel</li><li>0 – Not required</li></ul> | Bits 5:3 can be used to build logical                              |

| 4    | 0                | REQ_X | <ul><li>1 – Require trigger on X-channel</li><li>0 – Not required</li></ul> | AND operation between channels.                                    |

| 3    | 0                | REQ_Y | <ul><li>1 – Require trigger on Y-channel</li><li>0 – Not required</li></ul> | Example:<br>X and Y = Require<br>X and Y, ignore Z<br>→ 00 011 011 |

| 2    | 1                | EN_Z  | <ul><li>1 – Enable trigger on Z-channel</li><li>0 – Not required</li></ul>  | Bits 2:0 can be used to build logical                              |

| 1    | 1                | EN_X  | <ul><li>1 – Enable trigger on X-channel</li><li>0 – Not required</li></ul>  | OR operation between channels.                                     |

| 0    | 1                | EN_Y  | <ul><li>1 – Enable trigger on Y-channel</li><li>0 – Not required</li></ul>  | Example:<br>X or Y = Disable Z<br>→ 00 000 011                     |

Address value: 00011

Register name: MD\_Y\_TH, Motion Detector Y-threshold (Indirect access via CTRL\_SEL)

| Bits | Initial<br>Value | Name | Description                                          |

|------|------------------|------|------------------------------------------------------|

| 7:0  | 10h              | Y_TH | Threshold for Y-acceleration change when MD is used. |

Address value: 00100

Register name: MD\_X\_TH, Motion Detector X-threshold (Indirect access via CTRL\_SEL)

|      |                  | _ ,  |                                                      |

|------|------------------|------|------------------------------------------------------|

| Bits | Initial<br>Value | Name | Description                                          |

| 7:0  | 10h              | X_TH | Threshold for X-acceleration change when MD is used. |

Address value: 00101

Register name: MD Z TH, Motion Detector Z-threshold (Indirect access via CTRL SEL)

| Bits | Initial<br>Value | Name | Description                                          |

|------|------------------|------|------------------------------------------------------|

| 7:0  | 10h              | Z_TH | Threshold for Z-acceleration change when MD is used. |

The bit level descriptions for registers MD\_X\_TH, MD\_Y\_TH and MD\_Z\_TH are presented in Table 10, Table 11 and Table 12 below. The threshold levels are in unsigned format and they are absolute values for the acceleration that triggers the motion detector interrupt. Values presented below are typical threshold values and they are not factory calibrated.

Table 10. Bit level description for motion detector typical threshold levels (SCA3000-D01 and SCA3000-D02).

|                                                            | Typical bit weights |      |      |     |     |     |     |    |

|------------------------------------------------------------|---------------------|------|------|-----|-----|-----|-----|----|

| Bit number                                                 | B7                  | B6   | B5   | B4  | В3  | B2  | B1  | B0 |

| SCA3000-D01, -D02<br>Acceleration [mg]<br>MD_X_TH, MD_TH_Z | Х                   | Х    | 1300 | 650 | 350 | 200 | 100 | 50 |

| SCA3000-D01, -D02<br>Acceleration [mg]<br>MD_Y_TH          | х                   | 1750 | 850  | 450 | 250 | 150 | 100 | 50 |

x = not used bit

Table 11. Bit level description for motion detector typical threshold levels (SCA3000-E01 and SCA3000-E02).

|                                                            | Typical bit weights |      |      |      |     |     |     |     |

|------------------------------------------------------------|---------------------|------|------|------|-----|-----|-----|-----|

| Bit number                                                 | B7                  | B6   | B5   | B4   | В3  | B2  | B1  | B0  |

| SCA3000-E01, -E02<br>Acceleration [mg]<br>MD_X_TH, MD_TH_Z | x                   | Х    | 2050 | 1050 | 550 | 300 | 150 | 100 |

| SCA3000-E01, -E02<br>Acceleration [mg]<br>MD_Y_TH          | х                   | 2700 | 1350 | 700  | 350 | 200 | 100 | 50  |

x = not used bit

Table 12. Bit level description for motion detector typical threshold levels (SCA3000-E04).

|                                                | Typical bit weights |      |      |      |      |     |     |     |  |

|------------------------------------------------|---------------------|------|------|------|------|-----|-----|-----|--|

| Bit number                                     | B7                  | B6   | B5   | B4   | В3   | B2  | B1  | B0  |  |

| SCA3000-E04 Acceleration [mg] MD_X_TH, MD_TH_Z | Х                   | Х    | 4100 | 2100 | 1100 | 600 | 300 | 200 |  |

| SCA3000-E04 Acceleration [mg] MD_Y_TH          | Х                   | 5400 | 2700 | 1400 | 700  | 400 | 200 | 100 |  |

x = not used bit

Address value: 01011

Register name: OUT\_CTRL, Output configuration (Indirect access via CTRL\_SEL)

| Bits | Initial<br>Value | Name     | Description                                                                                                                                                                                                               |

|------|------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5  |                  |          | Reserved                                                                                                                                                                                                                  |

| 4    | 1                | BUF_X_EN | Store X-axis acceleration data to ring buffer 1 – enabled 0 – disabled                                                                                                                                                    |

| 3    | 1                | BUF_Y_EN | Store Y-axis acceleration data to ring buffer 1 – enabled 0 – disabled                                                                                                                                                    |

| 2    | 1                | BUF_Z_EN | Store Z-axis acceleration data to ring buffer 1 – enabled 0 – disabled                                                                                                                                                    |

| 1:0  | 00               | BUF_RATE | Additional data rate reduction after calibration before data is loaded to ring buffer (no effect on output registers data rate) 11 – No rate reduction 10 – divide rate by 4 01 – divide rate by 2 00 – No rate reduction |

Address: 1Eh

Register name: UNLOCK, Unlock register lock

| Bits | Mode | Initial<br>Value | Name | Description                                                                                                                                                                     |

|------|------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | RW   | 00h              | KEY  | Lock can be opened by writing the following sequence into this register: 00h, 50h, A0h Writing any other sequence closes the lock. Lock state can be read from STATUS register. |

Address: 21h

Register name: INT\_MASK, HW interrupt mask register configures the operation of the INT pin.

| Bits | Mode | Initial<br>Value | Name     | Description                                                                                                                                                                      |

|------|------|------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | RW   | 0                | BUF_F_EN | Interrupt when output ring buffer is ¾ full<br>1 – Enabled<br>0 – Disabled                                                                                                       |

| 6    | RW   | 1                | BUF_H_EN | Interrupt when output ring buffer is ½ full 1 – Enabled 0 – Disabled                                                                                                             |

| 5:2  |      |                  |          | Reserved                                                                                                                                                                         |

| 1    | RW   | 0                | INT_ALL  | Mask all interrupts (only effects on the INT-pin)  1 – Mask all interrupts (including free fall detection and motion detector)  0 – Mask interrupts according to configured mode |

| 0    | RW   | 1                | INT_ACT  | INT-pin signal activity<br>1 – INT active high (INT-pin high)<br>0 – INT active low (INT-pin low)                                                                                |

Address: 22h

Register name: CTRL\_DATA, Control register data, UNLOCK REQUIRED

| Bits | Mode | Initial<br>Value | Name | Description                                                                                                                                                                                       |

|------|------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | RW   | 00h              | DATA | Data bits [7:0] of selected 8-bit control register. Write this register to actually perform the write operation to selected location. See register CTRL_SEL for information on register contents. |

#### 4 Serial Interfaces

Communication between the SCA3000 sensor and master controller is based on serial data transfer and a dedicated interrupt line (INT-pin). Two different serial interfaces are available for the SCA3000 sensor: SPI and  $I^2C$  (Phillips specification V2.1). However, only one per product is enabled by pre-programming in the factory. The SCA3000 acts as a slave on both the SPI and  $I^2C$  bus.

#### 4.1 SPI Interface

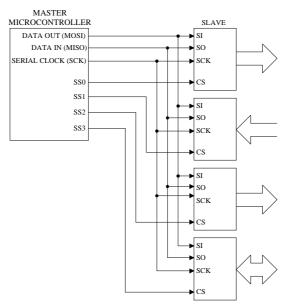

SPI bus is a full duplex synchronous 4-wire serial interface. It consists of one master device and one or more slave devices. The master is defined as a micro controller providing the SPI clock, and the slave as any integrated circuit receiving the SPI clock from the master. The SCA3000 sensor always operates as a slave device in master-slave operation mode. A typical SPI connection is presented in Figure 5.

Figure 5. Typical SPI connection.

The data transfer uses the following 4-wire interface:

| master out slave in      | $\mu C \rightarrow SCA3000$      |

|--------------------------|----------------------------------|

| master in slave out      | $SCA3000 \rightarrow \mu C$      |

| serial clock             | $\mu C \rightarrow SCA3000$      |

| chip select (low active) | $\mu C \rightarrow SCA3000$      |

|                          | master in slave out serial clock |

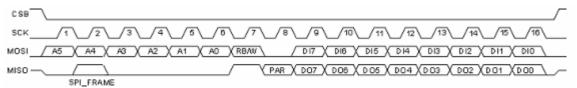

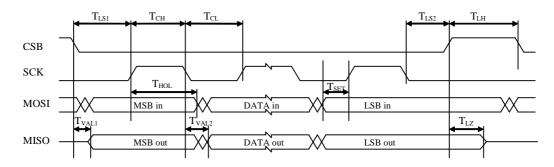

#### 4.1.1 SPI frame format

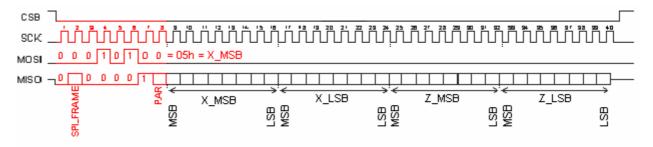

SCA3000 SPI frame format and transfer protocol is presented in Figure 6.

Figure 6. SPI frame format.

Each communication frame contains 16 bits. The first 8 bits in MOSI line contains info about the operation (read/write) and the register address being accessed. The first 6 bits define the 6 bit address for the selected operation, which is defined by bit 7 ('0' = read '1' = write), which is

followed by one zero bit. The later 8 bits in the MOSI line contain data for a write operation and are 'don't-care' for a read operation. Bits from MOSI line are sampled in on the rising edge of SCK and bits to MISO line are latched out on falling edge of SCK.

The first bits in the MISO line are the frame error bit (SPI\_FRAME, bit 2) of the previous SPI frame and odd parity bit (PAR, bit 8). Parity is calculated from data which is currently sent. Bit 7 is always '1'. The later 8 bits contain data for a read operation. During the write operation, these data bits are previous data bits of the addressed register.

For write commands, data is written into the addressed register on the rising edge of CSB. If the command frame is invalid as described in the section data will not be written into the register (please see "error conditioning" in section 4.1.2).

For read commands, data is latched into the internal SPI output register (shift register) on the 8th rising edge of SCK. The output register is shifted out MSB first over MISO output.

When the CSB is high state between data transfers, the MISO line is in the high-impedance state.

## 4.1.2 SPI bus error conditioning

While sending an SPI frame, if the CSB is raised to 1

- before sending 16 SCKs or

- the number of SCK pulses is not divisible by 8,

the frame error is activated and the frame is considered invalid. The status bit STATUS.SPI\_FRAME is set to indicate the frame error condition. During the next SPI, the frame error bit is sent out as SPI\_FRAME bit (see SPI\_FRAME in MISO line in Figure 6). STATUS.SPI\_FRAME bit is reset, if correct frame is received.

When an invalid frame is received, the last command is simply ignored and the register contents are left unchanged. If frame error happens while sending multiple samples in ring buffer mode, only the last output value is considered invalid.

## 4.1.3 Examples of SPI communication

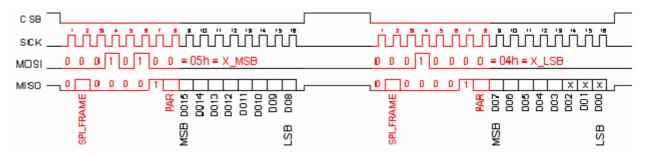

#### 4.1.3.1 Example of register read

An example of 11 bit X-axis acceleration read command is presented in Figure 7. The master gives the register address to be read via the MOSI line: '05' in hex format and '000101' in binary format, register name is X\_MSB (X-axis MSB frame). 7<sup>th</sup> bit is set to '0' to indicate the read operation.

The sensor replies to a requested operation by transferring the register content via MISO line. After transferring the asked X\_MSB register content, the master gives next register address to be read: '04' in hex format and '000100' in binary format, register name is X\_LSB (X-axis LSB frame). The sensor replies to the requested operation by transferring the register content MSB first.

Figure 7. An example of SPI read communication.

## 4.1.3.2 Example of decremented register read

Figure 8 presents a decremented read operation where the content of four output registers is read by one SPI frame. After normal register addressing and one register content reading, the  $\mu$ C keeps the CSB line low and continues supplying the SCK pulses. After every 8 SCK pulses, the output data address is decremented by one and the previous DOUT register's content is shifted out without parity bits. The parity bit in Figure 4 is calculated and transferred only for the first data frame. From the X\_LSB register address, the SCA3000 jumps to Z\_MSB. Decremented reading is possible only for registers X\_LSB ... Z\_MSB.

Figure 8. An example of decremented read operation.

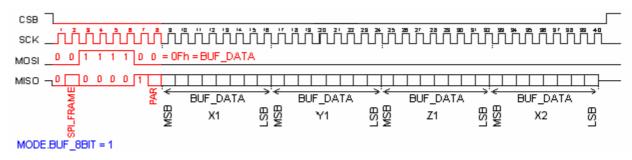

#### 4.1.3.3 Example of ring buffer read

An example of output ring buffer read by one SPI frame (ring buffer data length 8 bits) is presented in Figure 9. The whole ring buffer read procedure is very similar to decremented read described above. The output ring buffer is addressed (register name BUF\_DATA). The SCA3000 sensor continues shifting out the ring buffer content as long as  $\mu$ C continues supplying the SCK pulses.

Figure 9. An example of output ring buffer read operation.

## 4.2 I<sup>2</sup>C Interface

I<sup>2</sup>C is a 2-wire serial interface. It consists of one master device and one or more slave devices. The master is defined as a micro controller providing the serial clock (SCL), and the slave as any integrated circuit receiving the SCL clock from the master. The SCA3000 sensor always operates as a slave device in master-slave operation mode. When using an SPI interface, a hardware addressing is used (slaves have dedicated CSB signals), the I<sup>2</sup>C interface uses a software based addressing (slave devices have dedicated bit patterns as addresses).

The SCA3000 is compatible to the Philips I<sup>2</sup>C specification V2.1. Main used features of the I<sup>2</sup>C interface are:

- 10-bit addressing, SCA3000 I<sup>2</sup>C device address is 0x1F1

- Supports standard mode and fast mode

- Start / Restart / Stop

- Slave transceiver mode

- Designed for low power consumption

In addition to the Philips specification, the SCA3000 I<sup>2</sup>C interface supports multiple write and read mode.

#### 4.2.1 I<sup>2</sup>C frame format

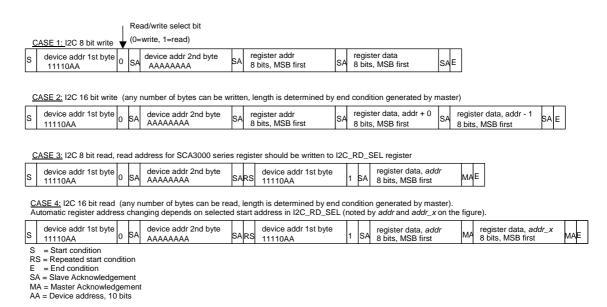

#### 4.2.1.1 I<sup>2</sup>C write mode

In I<sup>2</sup>C write mode, the first 8 bits after device address define the SCA3000 internal register address to be written. If multiple data words are transferred by the master, the register address is decreased automatically by one (see cases 1 and 2 in Figure 10).

#### 4.2.1.2 I<sup>2</sup>C read mode

The read mode operates as described in Philips I<sup>2</sup>C specification. I<sup>2</sup>C read operation returns the content of the register which address is defined in I2C\_RD\_SEL register. So when performing the I<sup>2</sup>C read operation, the register address to be read has to be written into I2C\_RD\_SEL register before actual read operation. Read operation starts from register address that has been written earlier in I2C\_RD\_SEL register. Read data is acknowledged by I<sup>2</sup>C master. Automatic read address change depends on the selected start address (see cases 3 and 4 in Figure 10).

- If address is some of registers between X\_LSB → Z\_MSB the register address is automatically cycled as follows:

- ...  $\rightarrow$  Y\_MSB  $\rightarrow$  Y\_LSB  $\rightarrow$  X\_MSB  $\rightarrow$  X\_LSB  $\rightarrow$  Z\_MSB  $\rightarrow$  Z\_LSB  $\rightarrow$  Y\_MSB  $\rightarrow$  Y\_LSB  $\rightarrow$  ...

- If the start address is any other register, the read address is NOT automatically incremented or decremented (the data transfer continues from the same address.) This enables the burst read from output ring buffer (register BUF\_DATA).

### 4.2.1.3 Decremented register read

Decremented reading is possible only for registers X\_LSB ... Z\_MSB. Refer to decremented read with SPI interface section 4.1.3.2.

## 4.2.2 Examples of I<sup>2</sup>C communication

Examples of I<sup>2</sup>C communication are presented below in Figure 10.

Figure 10. I<sup>2</sup>C frame format.

### 5 Electrical Characteristics

All voltages are reference to ground. Currents flowing into the circuit have positive values.

## 5.1 Absolute maximum ratings

The absolute maximum ratings of the SCA3000 are presented in Table 13 below.

Table 13. Absolute maximum ratings of the SCA3000

| Parameter                         | Value                      | Unit |

|-----------------------------------|----------------------------|------|

| Supply voltage (V <sub>dd</sub> ) | -0.3 to +3.6               | V    |

| Voltage at input / output pins    | $-0.3$ to $(V_{dd} + 0.3)$ | V    |

| ESD (Human body model)            | ±2                         | kV   |

| Storage temperature               | -40 <b>+12</b> 5           | °C   |

| Storage / operating temperature   | -40 <b>+</b> 85            | °C   |

| Mechanical shock *                | > 10 000                   | g    |

| Ultrasonic cleaning               | Not all                    | owed |

<sup>\* 1</sup> m drop on concrete may cause >>10000 g shock.

## 5.2 Power Supply

Please refer to the corresponding product datasheet.

## 5.3 Digital I/O Specification

## 5.3.1 Digital I/O DC characteristics

Table 14. DC characteristics of digital I/O pins.

| No.  | Parameter                      | Conditions             | Symbol          | Min      | Тур | Max      | Unit |  |

|------|--------------------------------|------------------------|-----------------|----------|-----|----------|------|--|

|      | Input: CSB, MOSI, Xreset,      |                        |                 |          |     |          |      |  |

| SCK  | _SCL has no pull up / p        | oull down              |                 |          |     |          |      |  |

| 1    | Pull up current:<br>CSB        | $V_{IN} = 0 V$         | I <sub>PU</sub> | 10       |     | 50       | μΑ   |  |

| 2    | Pull down current:<br>MOSI     | $V_{IN} = Dvio$        | $I_{PD}$        | 10       |     | 50       | μΑ   |  |